基于FPGA的扩频测距快速捕获仿真研究

距离测量是测试技术中的一项基本测试技术,其几乎贯穿于工程实践的每个领域。在军事航天领域,由于其特殊的需求,对测距系统的量程、实时性和精度要求越来越高,而扩频测距由于其抗干扰能力强、精度高、作用范围广、隐蔽性好、适应性强、全天候等优势,在测距系统中得到了重视。

扩频测距也称伪码测距,它是采用一个较长周期的PN码序列作为发射信号,将它与目标反射或转发回来的PN码序列的相位进行比较,即比较两个码序列相差的码片数,从而看出其时间差,换算出发射机与目的地之间的距离。如果码片选得很窄,即码速率做得很高,那么就可以完成高精度的测距。但随着码速率的提高和码周期的加长,传统的捕获时间将达到不可容忍的地步,所以需要考虑快速捕获算法。

由扩频码的自相关函数可知,只有在t’=(t-τ)时,扩频解调输出V(t)的信号最大。根据τ就能算出两地的距离![]() ,c为电磁波传播速度。

,c为电磁波传播速度。

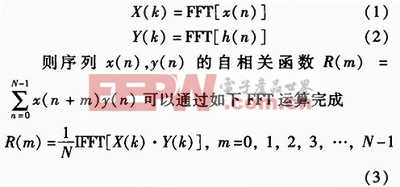

由于计算两序列的自相关函数![]() 需要用循环卷积代替自相关函数来计算扩频测距系统中的码片偏移,可以节省运算时间(大约为1/114),加快捕获过程。设x(n),y(n)分别为现有发射PN码与反射回来的PN码,序列长度为N,对它们分别做N点FFT,记

需要用循环卷积代替自相关函数来计算扩频测距系统中的码片偏移,可以节省运算时间(大约为1/114),加快捕获过程。设x(n),y(n)分别为现有发射PN码与反射回来的PN码,序列长度为N,对它们分别做N点FFT,记

可知R(m)为现有发射PN码与反射回来的PN码之间的相关值序列,长度为N,可知当R(m)中最大值的序列号减1即为码片差。

1 仿真方案设计

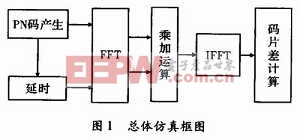

首先由m序列发生器产生出两路序列长度为N的PN码,其中一路经过延时模块以后与另一路分别进入FFT模块进行FFT运算,将进行FFT后的两组数据运算后进入IFFT模块得出序列组,由序列组得出两路序列之间的码片偏移数,从而算出其时延。系统总体框图如图1所示。

评论