基于FPGA的数字示波器

摘要:提出一种基于FPGA的简易数字示波器设计方法,硬件上采用以Altera公司的EP2C8Q208CN现场可编程门阵列芯片作为核心器件,同时结合FPGA和NIOS软核的优势,设计高效的片上可编程系统(SoPC)对高速A/D所采集的数据进行快速存储和处理。整机测试表明,系统各功能正常,整个系统集成度高,体积小,可靠性高,易于程控,使用灵活。

关键词:现场可编程逻辑门阵列;信号调整;高速A/D;片上可编程系统

高速数字化采样技术和FPGA技术的发展对传统测试仪器的体系结构,包括传统测量方法、传统仪器的定义和分类等都产生深刻的影响。伴随数字技术的发展,数字示波器展现了其强大的功能:智能捕获、参数分析、时频等变换处理、超大规模数据波形存储以及数据上网共享等。与传统模拟示波器相比,数字示波器不仅具有可存储波形,体积小,功耗低,使用方便等优点,而且还具有强大的信号实时处理分析功能。

1 系统组成

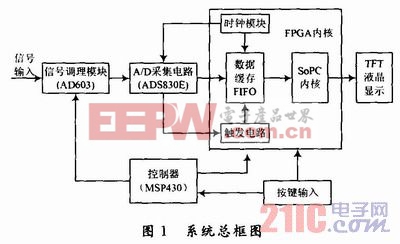

设计的数字示波器总体框图如图1所示。

系统主要包括信号调理模块、A/D转换模块、控制器模块、时钟产生模块、触发电路、数据缓存模块、数据快速处理模块、输入模块及显示模块。控制器模块由MSP430单片机组成,用来控制信号调理模块和A/D转换模块以及按键输入;时钟产生模块、数据缓存模块,数据快速处理模块这三个部分在FPGA内部完成;数据快速处理模块是由基于FPGA的SoPC来完成的,同时SoPC还控制TFT液晶的显示。

2 系统理论分析及硬件实现

2.1 信号调理模块

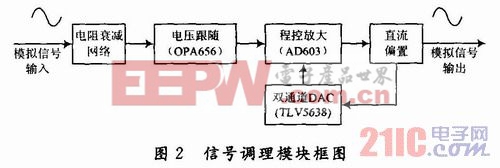

信号调理电路包括衰减网络、电压跟随电路、程控放大电路和直流偏置电路等。信号调理电路框图如图2所示。

为了保证输入信号在AD芯片的参考电压范围内,当大信号输入时,必须通过衰减网络对其进行衰减,以满足A/D采集电路的电压要求。通过电阻网络分压实现信号的衰减,衰减倍数有1/2和1/20两种,通过单片机控制继电器(TQ2-5),实现对两种衰减倍数的切换;另外,电容网络是进行相位补偿,通过可调电容可以实现相位的补偿。电压跟随电路作为隔离级,可减小后级电路对前级电路的影响。电压跟随电路由TI公司的OPA656构成,OPA656是宽带单位增益稳定FET输入运算放大器。

程控放大电路由程控增益芯片AD603和双通道串口数/模转换器TLV5638组成。单片机通过控制TLV5638的通道A产生高精度模拟电压,用于调节AD603的放大倍数。直流偏置电路中,单片机控制TLV5638,使其OUTB引脚输出一个直流电压,该电压经过NE5532组成的等比例反向器后接到OPA656的反向输入端,可以通过这个电压来确定OPA656的输出,反映到屏幕上是波形的中线位置。如果液晶显示的波形偏下或者偏上,可以调节TLV5638的B端输出来调节。

评论