基于CPLD的I2C总线接口设计

I2C总线是两线式串行总线,用于连接微控制器及其外围设备。该总线具有如下特点:1)只要求两条总线线路,一条串行数据线(SDA),一条串行时钟线(SDL);2)每个连接到总线的器件都可以通过唯一的地址寻址,总线中主机可以作为主机发送器或主机接收器;3)它是一个真正的多主机总线,如果两个或更多主机同时初始化数据传输可以通过冲突检测和仲裁防止数据被破坏;4)双向数据传输位速率在标准模式下可达100 kbit/s快速模式下可达400kbit/s高速模式下可达3.4 Mbit/s;5)片上的滤波器可以滤去总线数据线上的毛刺以保证数据完整;6)连接到相同总线的IC数量只受到总线的最大电容400 pF限制。I2C总线最主要的优点是其简单性和有效性。由于I2C总线为两线式总线,它占用的空间非常小,减少了电路板的空间和芯片管脚的数量,降低了互联成本。它支持多主控制(multimastering),总线中任何能够进行发送和接收的设备都可以成为主机。任何主机都能够控制总线信号的传输和时钟频率。在任何时间点上只能有一个器件作为主机,其他器件作为从机。正是由于I2C总线具有上述诸多优点,具备I2C接口的器件在仪器设计中已被广泛采用,比较常见的如:日历芯片、存储芯片、模数转换器以及数模转换器等。

不幸的是大多数CPU都擅长操作并口,而并不具备直接操作I2C总线接口的能力。在系统设计时,为了与具有I2C总线接口的芯片连接,经常采用的方法是:利用CPU的2条通用输入输出(GPIO)线作为I2C总线使用,用软件模拟的方法,产生I2C总线需要的控制时序。该方法虽然可以达到同I2C器件连接的目的,却不可避免地带来软件编制复杂、占用CPU处理时间多的弊端。为了在不增加编程难度、不大量占用CPU处理时间的前提下使不具备I2C总线的CPU也能够充分享受I2C总线的优点,本文设计了一种基于CPLD的8位并行接口转I2C总线接口的控制模块,通过该模块,具有并口的CPU可以通过对并口的读写完成对I2C总线的控制。

1 I2C总线的基本时序

I2C总线是由数据线SDA和时钟线SCL构成,靠它们在连接于I2C总线的各个设备之间传送信息。I2C总线在传送数据过程中共有4种类型的信号,分别是:开始信号、结束信号、应答信号和数据传输信号。

开始信号:主机控制SDA信号线在SCL线的高电平期间发生由高电平到低电平的跳变,通知从机开始数据传输。

结束信号:主机控制SDA信号线在SCL线的高电平期间发生由低电平到高电平的跳变,通知从机本次数据传输结束。

应答信号:接收数据的芯片(主机或者从机)在完整接收到8位数据后,向发送数据的芯片发出低电平信号,通知发送的数据已被接收。发送数据的芯片应根据应答信号的电平高低判断数据是否被接收芯片接收。

数据传输信号:发送数据的芯片在SCL脉冲控制下在SDA上串行输出数据信号,SDA只能在SCL为低电平期间改变状态,在SCL为高电平期间应保持稳定。

I2C总线上的数据传输主要有4种模式,分别是:字节写、页面写、当前地址读、随机地址读和顺序读。

字节写:对给定的芯片的确定地址单元写入一个字节的数据。

页面写:对给定的芯片的确定地址单元所在页面连续写入全部的数据。

当前地址读:读出当前地址单元中的一个字节数据。

随机地址读:从给定的芯片的确定地址单元中读出一个字节数据。

顺序读:从给定的地址后连续读出n个字节的数据。

I2C总线各种信号及数据传输模式示意图如图1所示。

利用CPLD设计一种模块,如果能够将CPU发出的并行数据按上述I2C总线数据传输模式自动转换成串行数据输出,同时将接收到的I2C总线串行数据自动转换成并行数据供CPU读取,则不具备I2C总线接口的CPU也能通过对并口的操作轻松实现与I2C总线连接并同其他具备I2C总线接口的芯片交换数据。为此本文设计了一种基于CPLD的工作于I2C总线主机模式的并口转I2C总线模块。利用该模块CPU可以很容易地实现与I2C总线的接口。

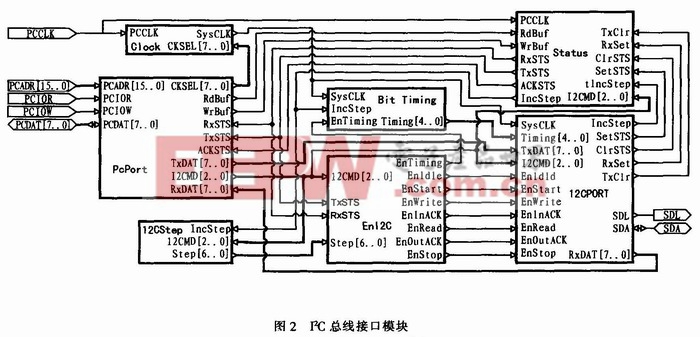

2 I2C总线接口模块的CPLD实现

上面简要介绍了I2C总线的信号以及I2C总线的数据传输模式,如果要使接口模块正常工作,CPU必须首先要通知模块执行什么操作,而后再把需要的数据依次送入模块中,考虑到I2C总线的速率可以在0~3.4 Mbit/s之间,为了适应不同外设的需要,模块还应在CPU的控制下自由调整数据传送速率。因此,CPU应能够向模块发送数据传送速率控制数据、I2C总线工作模式控制数据、信息交换数据,同时还能从模块

中读取工作状态数据、模块接收数据。据此设计出基于CPLD的I2C总线接口模块如图2所示。

评论