基于CPLD的I2C总线接口设计

该设计由7个单元组成,它们分别是:用于调整I2C总线数据传输速率的Clock单元;用于实现同CPU并行接口的PcPort单元:用于产生I2C总线工作时序的I2CStep单元;用于产生数据传输时序的BitTiming单元;用于产生I2C总线使能信号的En12C单元:用于产生I2C总线接口模块工作状态指示的Status单元:以及用于产生I2C接口时钟信号SDL和数据串行输入输出信号SDA的I2CPORT单元。

2.1 Clock单元

整个接口模块以CPU的系统时钟作为主时钟信号,模块传输数据的速率受该时钟频率的控制,时钟频率高则模块传输数据的速率也高,反之亦然。考虑到各种具有I2C总线接口的芯片的工作速率差别较大(从几十kB/s到几MB/s),该接口模块的工作速率必须能够灵活调整,以适应不同外设芯片的接口需要。

Clock单元实际上就是一个分频器,它在输出频率控制码CKSEL[7..0]的控制下产生对PCCLK分频后合适的时钟信号供I2C接口使用。

2.2 I2CStep单元

通过对图1中I2C总线各种工作模式的分析,可知不同的工作模式都是按特定的工作流程串行输入、输出数据的,例如字节写模式的工作流程为:发送开始信号、串行输出被叫芯片的片选地址、发送写信号、等待被叫芯片响应、串行输出被叫芯片存储单元的地址、等待被叫芯片响应、串行输出写入的数据、等待被叫芯片响应、发送结束信号结束本次操作。

为了使接口模块正确工作,模块在接收到来自CPU的工作模式控制信号I2CMD[2..0]后,根据工作模式的不同产生接口模块工作流程。当前流程结束后由Status单元产生IncStep信号,控制工作流程指向下一阶段。该模块的功能类似一个计数器,它在I2CMD[2..0]和I2CStep的共同作用下,产生长度不等的工作流程信号Step[6..0]。

2.3 BitTiming单元

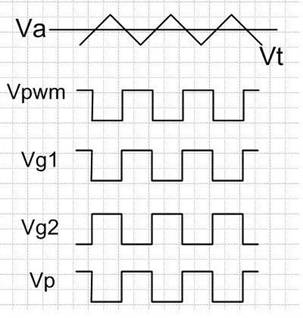

在I2C总线工作流程的不同阶段,I2C接口模块需要按一定的时序完成不同的工作,通过对总线数据传输模式的分析可知,在一个数据传输模式的所有工作流程中,输入、输出8位数据的工作流程用时最长,需要25个工作时序周期,为了满足所有工作流程的需要,工作时序Bit-Timing单元被设计成最长可产生31个时钟周期的工作时序。

该单元在IncStep=‘1’时复位工作时序;在EnTiming信号有效后的每个SysCLK的上升沿使工作时序信号EnTiming加1,用于控制I2CPORT单元按给定的时序串行输入、输出数据信息。

2.4 Status单元

在I2C总线工作过程中,CPU需要随时了解I2C接口模块的发送数据寄存器是否为空、接收数据寄存器是否准备数据好、从机响应信号是否正确、当前工作流程是否完成等工作状态,只有在发送数据寄存器为空时,CPU才可以向接口模块写入待传输数据;只有在接收数据寄存器数据准备好后,CPU才可以从接口模块读入正确的接收数据;从机响应信号不正确时,CPU应立即发出结束信号结束本次操作;当前工作流程未完成前不能进行下一流程。这些状态信号全部由Status单元产生。

在该单元中,共有4种输出信号,它们分别是:用于指示发送数据寄存器是否为空的TxSTS状态,该状态在CPU写入数据后置‘1’,数据被发送后清‘0’;用于指示接收数据准备好状态的RxSTS信号,该信号在模块接收到完整的数据后置‘1’,数据被CPU读走后清‘0’;用于指示模块工作状态的ACKSTS信号,该信号在模块工作正常(接收到从机响应信号)时自动置‘1’,工作不正常时自动清‘0’;用于使工作流程指向下一阶段的IncStep信号,该信号在当前工作流程完成后由模块自动产生,用于使模块的工作流程指向下一阶段。

2.5 EnI2C单元

在I2C总线接口模块中,BitTiming单元何时开始产生工作时序,需要时序信号控制,I2CPORT单元何时向I2C总线输出信息、何时从I2C总线上读入信息也需要时序信号控制。这些控制时序的产生由EnI2C单元完成。

EnI2C单元在I2CMD[2..0]、Step[6..0]、TxSTS、RxSTS等信号的控制下,从预先存储于单元内部的一组I2C工作时序信息中读出当前的时序信息输出,控制BitTiming和I2CPORT单元工作。

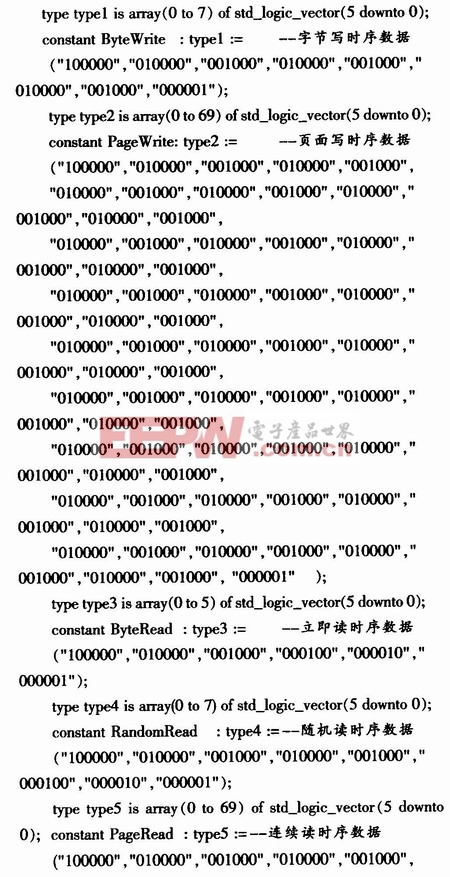

模块中,预先存储的I2C工作时序信息实现如下:

评论