基于CPLD的I2C总线接口设计

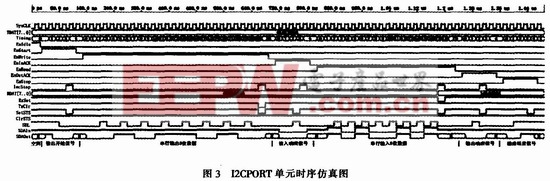

2.6 12CPORT单元

本单元是整个设计的核心,用于完成数据的I2C总线输出以及I2C总线输入数据的读入。同时产生接口模块的各种工作状态。

该单元的工作过程为:在SysCLK的下降沿分别读入工作使能信号和工作时序信号,如果此时EnIdle=‘1’则强制I2C总线进入空闲模式;如果EnStart=‘1’,则使I2C总线输出开始信号;如果EnWrite=‘1’,则使I2C总线输出8位数据信号;如果EnInACK=‘1’,则从I2C总线读入从机响应信号;如果EnRead=‘1’,则从I2C总线读入8位数据;如果EnOutACK=‘1’。则使I2C总线输出主机响应信号;如果EnStop=‘1’,则使I2C总线输出结束信号;在整个工作过程中,模块会自动根据工作情况,设置各种状态控制信号。

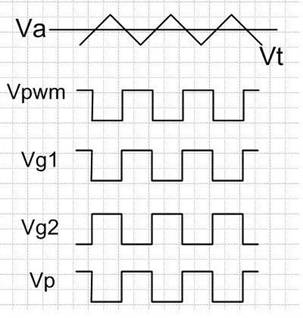

图3是用QuartusII9.0对该单元仿真的时序图。本文引用地址:http://www.eepw.com.cn/article/191294.htm

2.7 PcPort单元的实现

该单元是模块与CPU的接口,CPU通过该单元向接口模块写入工作模式控制信息、需要发送的数据以及I2C工作速度控制信息;同时通过该单元读入从机响应信息、从机输出数据、发送接收寄存器状态等信息。

评论