一种基于SoPC的FPGA在线测试方法

摘要:针对Altera公司现有FPGA在线测试方法无法适应大批量测试/激励数据自动传输的情况,论文提出了一种基于SoPC的FPGA在线测试方法,该方法采用Nios II控制数据传输过程、DMA协助数据传输、FIFO作为数据暂存,采用自定义外设完成了DMA模块与FIFO的接口设计,从而DMA可以直接操作FIFO,测试结果表明该方法是一种可行且高效的FPGA在线测试方法。创新性在于充分利用JTAG接口完成FPGA的在线测试,同时测试数据能够写入PC中的文件/激励数据从文件读出。

关键词:在线测试:SoPC;DMA;Host-Base File System

可编程逻辑器件供应商Altera公司针对FPGA的开发推出了6种系统在线测试方法:SignalTapⅡ、SignalProbe、Logic Analyzer Inter-face、In-System Sources and Probes、In-System Memory Content Editor以及Virtual JTAG。上述各种在线测试方法中,只有最后两种方法允许PC和FPGA进行基于文件的数据交互。而In-System Memory Content Editor只允许用户手动更新FPGA片上RAM的内容,不利于测试数据的大规模自动采集和传输。Virtual JTAG虽然可以实现测试数据采集和传输的自动控制,但是需要利用TCL接口函数编写代码,而且要求用户对JTAG有深入的了解,增大了开发难度。本文提出了一种基于SoPC的FPGA在线测试方法,是对现有FPGA在线测试方法的一种有效的补充。

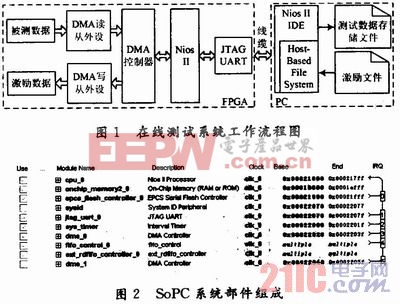

1 在线测试数据操作流程

基于SoPC的FPGA在线测试方法的数据操作流程如图1所示。如果用户需要采集FPGA的测试数据并且上传至PC机,则用户首先要将被测试数据写入DMA读从外设,然后系统自动启动DMA控制器,将数据送入Nios II的数据存储器。再由JTAG UART控制器经JTAG接口上传至Nios II IDE(NiosⅡIntegrated Development Environment,Nios II开发环境),Nios II IDE将接收到的数据写入测量数据存储文件,从而完成了FPGA测试数据的上传。如果用户需要将PC机中的激励数据文件下载至FPGA,则系统首先在Nios II IDE中通过Host-Based File System读出激励文件数据,然后由JTAG接口经JTAG UART控制器下载至Nios II处理器的数据存储器,Nios II发起DMA写传输把数据从数据存储器搬运至DMA写从外设并写入FPGA片上FIFO,从而完成了激励数据的下载。

评论