基于FPGA高速并行采样技术的研究

摘要:介绍一种基于四通道ADC的高速交错采样设计方法以及在FPGA平台上的实现。着重阐述四通道高速采样时钟的设计与实现、高速数据的同步接收以及采样数据的校正算法。实验及仿真结果表明,同步数据采集的结构设计和预处理算法,能良好抑制并行ADC输出信号因相位偏移、时钟抖动等造成的失配误差。

关键词:交错采样;高速采样时钟;同步接收;信号处理

0 引言

高速、超宽带信号采集技术在雷达、天文和气象等领域应用广泛。高采样率需要高速的模/数转换器(ADC)。目前市场上单片高速ADC的价格昂贵,分辨率较低,且采用单片超高速ADC实现的数据采集对FPGA的性能和PCB布局布线技术提出了严峻的挑战。

利用时间交叉采样原理,对同一信号用多个相对较低速的ADC并行采样是可行的。本文针对某项目要求构建了四路采样率为400 MHz的ADC和高性能FPGA接口处理平台,实现1.6 GHz数据采集。着重讨论了ADC采样时钟的设计、数据同步接收和校正预处理等关键技术,并提出软硬件优化方案。

1 采样系统设计

1.1 多ADC并行采样原理

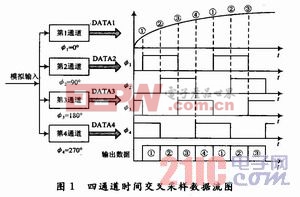

时间交叉采样原理基于使用多片相对低速的并行ADC实现高速数据采集。m路ADC中每一片ADC的采样频率是整个系统采样频率的1/m,通过算法调整可使每一路通道时钟具有固定相位差,采样数据经多路排序合并后,可达到一路ADC采样速率m倍的效果。图1是四路采样时序结构,理想条件下各路时钟相位依次相差90°。

1.2 时钟设计

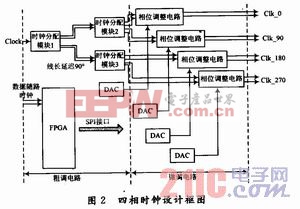

外部时钟信号经“时钟分配模块1”转换成两路同相差分时钟信号,一路送“时钟分配模块2”,另一路经PCB走线移相90°后送“时钟分配模块3”。模块2,3各输出两路180°相差时钟信号,最终得到依次相差近似90°的四路ADC采样时钟。

四路时钟信号并非严格均匀相差90°,各路独立进入“相位调整电路”微调。相位微调电路由可编程移相LC网络组成,FPGA独立控制四路调整电路,使相位时延控制在200~300 ps范围。时钟分配及调整电路结构如图2所示。

评论