基于FPGA的CAN总线控制器设计

摘要:使用Verilog HDL硬件描述语言完成了对CAN总线控制器的设计,能够实现符合CAN2.0A协议的所有功能。本总线控制器的外部接口采用Altera公司开发的Avalon总线接口,增强了控制器的应用灵活性。本设计使用Modelsim软件完成了功能仿真和时序仿真。

关键词:CAN总线;控制器;现场可编程门阵列

0 引言

CAN(控制器局域网)是一种先进的串行通信协议,由德国BOSCH公司开发,并最终成为国际标准(ISO11898),是国际上使用最广泛的现场总线之一。目前世界上已有20多家CAN总线控制器生产商,110多种CAN总线控制器芯片和集成CAN总线控制器的微处理器芯片。

由于定制的CAN总线控制器芯片不能嵌入到SoC(片上系统)中,而采用分立元器件实现CAN总线接口,使得系统中器件数量增加,同时也增大了系统面积,本文所介绍的CAN总线控制器正是由Verilog HDL语言描述,既可以作为一个独立的设备,也可以作为一个模块集成到FPGA中。

虽然目前国内外已有很多人研究或设计了CAN总线控制器IP核,但其中大多数只是对控制器中的某一个模块进行了研究和设计,并没有实现一个完整的CAN总线控制器的功能,例如文献只对CAN控制器的状态机进行研究,文献只对CAN控制器的位定时模块进行研究。而完整实现了CAN总线控制器功能的作品中,最高工作频率又不是很理想,例如Mentor Graphics公司提供的MCAN2D1 CAN2.0 Network Controller的最高工作频率只有32.46MHz,文献中介绍的CAN总线控制器的最高工作频率也只有50MHz,这些IP核显然不能适应高速环境的要求,同时文献中介绍的控制器对外接口中出现了寄存器使能位等接口,这种接口不符合Avalon总线规范,不利于集成到FPGA芯片中,其通用性肯定较差,所以研究并设计出一款高速且通用性强的CAN总线控制器的IP核仍然是有其重要意义的。

1 系统实现

1.1 系统框图

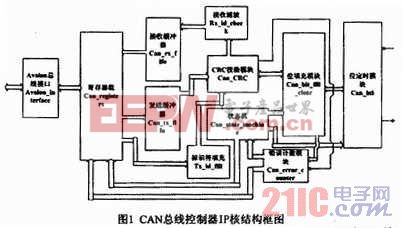

本设计中将整个CAN控制器系统分为了11个模块,分别是Avalon总线接口模块、寄存器组模块、接收缓冲器模块、发送缓冲器模块、接收滤波模块、CRC校验模块、状态机模块、标识符填充模块、错误计数器模块、位填充模块、位定时模块。其结构框图如图1所示。

评论