基于CPLD/FPGA的USB读写控制器

引言

随着计算机科技的发展,无纸办公日益成为各单位日常办公的主要形式。而随着USB存储设备日益广泛的使用,数据泄漏的危害也越来越严重。因此在单位内部对USB存储设备的操作权限进行控制是很有必要的。

本设计可将不同的USB存储设备(包括安全存储设备和普通存储设备)通过不同的接口接入到主机上,同时对主机和设备问传输的数据进行提取,分析和拦截。其应用范围比较广泛,为了方便介绍,本文将其作为USB存储设备管理系统的一部分,根据具体的应用来介绍控制器的设计原理。读写控制器可应用在对PC机与安全存储设备和普通存储设备的数据共享管理上。其中,PC机的数据要求被保护,安全设备的使用权限被严格控制,不会泄漏数据;而普通设备则没有采取任何安全措施,很有可能向外泄漏数据,比如通用的U盘。

控制器的主要功能是通过不同的接口把两种USB存储设备区分开来,实时监测PC机和普通设备间的数据,当检测到PC机向普通设备写入数据包时,对其强行破坏,防止数据泄漏。

1 硬件原理

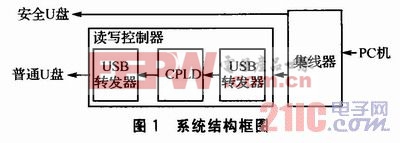

系统的结构框图如图1所示。集线器芯片将上游一路USB总线分为两路:一路直接通过专用的USB接口与安全存储设备连接,另一路通过读写控制器和普通存储设备连接。读写控制器采用CPLD、USB转发器以及外围电路实现集线器和普通存储设备的连接。在CPLD中设计逻辑电路实现对USB转发器传输方向的控制,并对数据进行分析和拦截,以破坏从PC机向普通USB存储设备传输的数据,防止泄漏。

集线器采用的是带有4个下游端口的GL850G。其端口传输的是USB总线的差分信号,故将其上游端口直接接PC机,下游端口接安全USB存储设备或读写控制器。

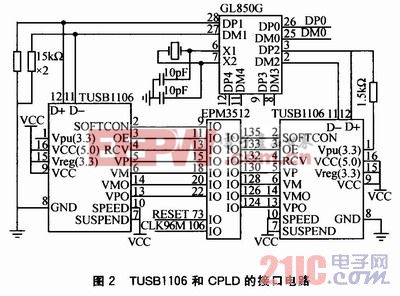

读写控制器是由1片CPLD和2片USB转发器及其外围电路组成。CPLD采用的是Altera公司的EPM3512。它具有10000个可用的门、512个宏单元、208个可用的I/O引脚,调试和升级简便,开发十分灵活。市场上关于USB转接的芯片很多,本文设计的读写控制器要求功能简单、性能稳定,因此USB转发器采用TI公司的TUSB1106,既满足设计的要求,也不存在资源浪费。该芯片的详细介绍见参考文献。其中VP0、VM0引脚由CPLD驱动。VP、VM和RCV输人到CPLD中。TUSB1106和CPLD的接口电路如图2所示。

评论