基于FPGA的LCoS驱动和图像处理系统设计

摘要:针对分辨率为1 024×768的LCoS屏编写了Verilog HDL驱动代码,在quartusⅡ9.1平台上综合编译,并在Altera的FPGA芯片EP3C5E14 4C8上进行了功能验证和实际输出信号测量。采用异步FIFO结构解决了跨异步时钟域的数据传输问题。嵌入FFT IP核后,可进一步对图像进行基于FFT的变换处理,分析图像的频谱。为计算全息3D图像处理及显示提供了硬件平台。

关键词:Verilog HDL;LCoS;异步FIFO;FFT

0 引言

基于空间光调制器的计算全息三维显示技术,目前常采用透射式LCD和反射式LCoS作为空间光调制器,以改变光经过空间光调制器(SLM)后的空间相位和振幅分布,达到对光信息的调制。传统的基于透射式LCD空间光调制器的计算全息三维显示系统,其成像光路复杂,而且必须依赖计算机进行数据发生、采集以及处理,这就限制了系统应用的灵活性,不便于推广。

相较于透射式LCD,LCoS具有光利用率高、体积小、开口率高、器件尺寸小等特点,可以很容易地实现高分辨率和微显示投影。采用彩色LCoS屏显示基于RGB的彩色图像,经过光学成像系统投影到接收屏上,实现计算全息图像的三维显示。

基于FPGA的显示系统有以下优势:第一,LCoS尺寸小,便于实现微投影,利用可灵活编程的FPGA器件作为驱动控制器,这样就可以将其做成像普通投影仪一样的微型投影设备,使计算全息三维显示摆脱了计算机和复杂光路的束缚,具有了更高的灵活性,为其走出实验室提供了条件。第二,因为在传统空间光调制器上得到的图像里含有物波和参考光的复共轭像,形成了噪声,在FPGA上可以实现图像滤波去噪,使得到的图像更清晰。第三,FPGA是基于可编程逻辑单元的器件,当经过综合、布局布线、时钟约束的代码烧录到FPGA器件后,FPGA就将算法代码硬件化了,可以作为专用芯片工作,其内部信号延时完全是硬件级传输延时。在处理数据搬移和复杂的数学运算以及一些循环操作时,例如图像的FFT变换,FPGA硬件运算要比软件运算快得多,即利用FPGA器件实现对软件算法的硬件加速。

基于以上原因,本文设计了基于FPGA的LCoS驱动代码及图像的FFT变换系统,为计算全息三维显示图像处理和显示提供了硬件平台。

1 系统设计

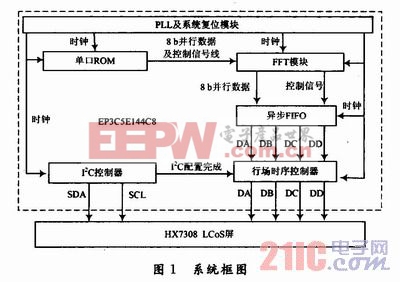

1.1 系统模块框图:

该系统采用cycloneⅢEP3C5E144C8,该芯片有5 136个LE,95个用户I/O,2个PLL,以及46个嵌入式乘法器和423 936 b的内部逻辑寄存器。以它丰富的资源,完全可以作为LCoS的驱动控制器件。显示屏采用Himax的反射式LCoS屏HX7308,其分辨率为1 024×768,可以支持256级灰度显示,具有内置的行场驱动电路,在外部输入时钟的上升沿和下降沿分别接收8b×4dots图像数据,这保证了场频可高达360 Hz。

系统的整体框图如图1所示。

评论