一种基于AT25T1024 FLASH的高速SPI接口设计

摘要:从一种军用板卡的实际需求出发,对SPI接口在设计中有诸如FPGA资源和管脚等限制的情况下,快速加栽配置数据的方法进行了分析。并基于ATMEL公司的AT25F1024 FLASH器件,描述了高速SPI接口的设计原理和方法,具有一定的实用性和可行性。

关键词:SPI;FIASH;军用板卡;FPGA;AT25T1024

0 引言

在一些军用芯片的早期设计中,一般先采用比较成熟的商用协议芯片进行军用化改造(通常做成板卡形式),而商用芯片的军用化改造主要体现在确定性、实时性、稳定性、安全性等问题上,所以一般需要在商用协议芯片的上层加入较多的控制功能。FPGA以其资源丰富,易于组织流水和并行处理等优点,为这种复杂控制提供了很好的选择。而SPI在芯片的管脚上只占用四根线,节约了芯片的管脚,同时为PCB的布局上节省空间,因此在基于FPGA的读写接口设计中,高速SPI是一种很好的选择。

1 SPI结构

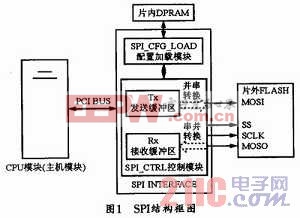

SPI (Serial Peripheral Interface-串行外围设备接口)是Motorola公司推出的一种高效率全双工同步串行数据接口,以主从模式工作,广泛应用于FLASH,实时时钟,AD转换器等。SPI串行外围设备总线根据串行同步时钟极性(CPOL)和时钟相位(CPHA)两个参数的设置分为四种工作方式(SPO,SP1,SP2,SP3)。本板卡选用的片外存储器AT25F1024仅支持0和3模式,为简化设计,本设计的SPI时钟采用SP0模式(CP-OL=0,CPHA=0),时钟极性为低电平,时钟相位串行时钟上升沿采样数据,下降沿数据输出.SPI为主从工作方式,主设备由三部分构成,SPI_CFG_LOAD配置加载模块可自动读取存储器FLASH的值,并加载到片内DPRAM中。主机通过配置SPI_CTRL控制模块相应的寄存器,来完成对片外FLASH的访问。SPI结构框图如图1所示。

2 高速SPI接口设计

2.1 配置加载模块的设计

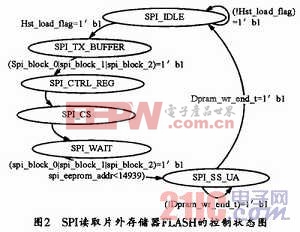

SPI_CFG_LOAD配置加载模块主要完成从片外FLASH读取数据,并将数据存入片内DPRAM中的功能。图2给出了对应的状态机设计。

评论