基于FPGA的实时中值滤波器硬件实现

高清视频监控逐渐成为市场的热点,视频监控不仅要求把现场图像捕获并保存,而且还要尽可能清晰。在高清图像的生成和采集过程中,往往会受到各种噪声的干扰,使高清图像的质量变差,因此必须对图像进行滤波、平滑等预处理来消除噪声。中值滤波作为一种非线性滤波方法,既可以消除随机噪声和脉冲干扰,又可以很大程度地保留图像的边缘信息,得到了广泛的运用。在许多实际应用场合,如高清视频监控、X光图像的降噪等,需要快速且实时地进行中值滤波,软件实现达不到实时处理的要求,因此选用硬件实现。

在硬件实现上,文献[1]、[2]等采用行延迟的方法形成邻域数据,以实现3×3的中值滤波。文献[7]为了提高红外成像跟踪器设计了大窗口的中值滤波器。文献[3]、[4]提出了邻域图像帧存的存储结构,该结构充分利用了图像帧存的数据结构转换特性,并行高速提供邻域图像数据,配以FPGA作为并行处理器,高速实时地实现了中值滤波。但是以上研究都是基于标清图像的中值滤波器,处理的图像大小一般为256×256、512×512的灰度图等,很少有实现高清图像的中值滤波器。本文在文献[3]、[4]的理论基础上,在苏光大主持研制成功的NIPC-3邻域图像并行处理机上实时实现了1 920×1 080×8 bit的高清图像的中值滤波器。该系统的硬件是基于一个标准的PCI板卡,Altera公司的CycloneII FPGA是图像处理系统的核心,此外,该板卡还包括了若干片SRAM、视频采集转换芯片、CPLD和PCI接口芯片。NIPC-3硬件处理的结果由PCI传到计算机做后续处理,是软硬件结合的系统。

1 快速二维中值滤波器算法

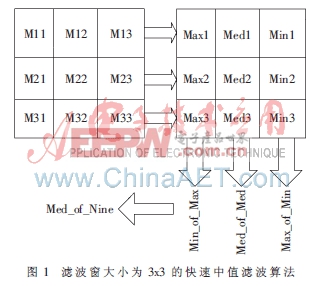

本文中值滤波器排序算法用文献[2]提出的快速排序算法。如图1,将3×3窗口内的各个像素分别定义为M11、M12、M13、M21、M22、M23、M31、M32、M33。首先分别对窗口中的每一行计算最大值、中值,最小值不难判断。9个数值中,3个最大值中的最大值和3个最小值中的最小值一定是9个像素中的最大值和最小值;3个中值中的最大值至少大于5个像素:即本行中的最小值和其他2行的中值及最小值;而3个中值中的最小值至少小于5个像素:即本行中的最大值和其他两行中的中值及最小值。最后,比较3个最大值中的最小值Min_of_Max,3个中值中的中值Med_of_Med,3个最小值中的最大值Max_of_Min,得到中间值即为滤波的最后结果Med_of_Nine。

利用这种排序法的中值滤波运算仅需17次比较,且该算法十分适用于在FPGA上做并行处理,大大提高了滤波的速度。

2 FPGA硬件实现

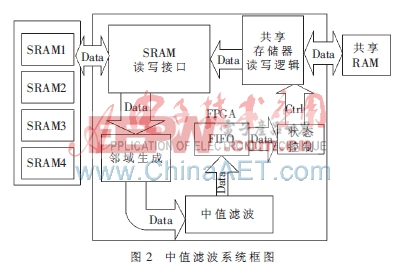

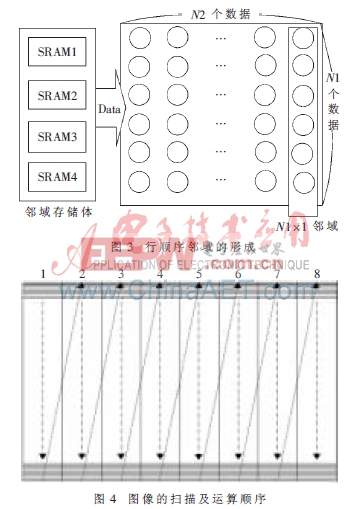

邻域图像并行处理机是一种以邻域图像帧存提供邻域图像数据、以邻域图像处理器并行邻域图像处理的图像并行处理机,其本质是邻域数据(即多数据)的并行处理[4]。中值滤波系统框图如图2所示,主机通过PCI接口将待处理数据写入共享RAM,数据再由共享RAM转入邻域存储体,利用行顺序邻域生成方法[3],将数据由串行转化为并行,实现处理并行,达到数据的高速处理。邻域存储体是由4片SRAM组成,型号是IS61SP6464,位宽为64 bit,一次可以存取8个字节,4片SRAM并行排列,一个时钟周期最多可以吞吐32个字节。见图3,考虑一个N1×1的随机邻域,N2个时钟周期就可以得到N1×N2大小的邻域。然后再将中值滤波模块结果通过FIFO缓存写入共享RAM,传到PC机显示。

滤波器相关文章:滤波器原理

fpga相关文章:fpga是什么

滤波器相关文章:滤波器原理

电源滤波器相关文章:电源滤波器原理

评论