SoC用低电压SRAM技术

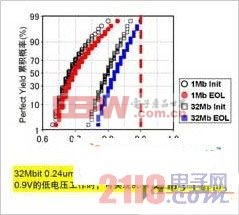

东芝在“2010 Symposium on VLSITechnology”上,发布了采用09年开始量产的40nm工艺SoC的低电压SRAM技术。该技术为主要用于便携产品及消费类产品的低功耗工艺技术。通过控制晶体管阈值电压的经时变化,可抑制SRAM的最小驱动电压上升。东芝此次证实,单元面积仅为0.24μm2的32MbitSRAM的驱动电压可在确保95%以上成品率的情况下降至0.9V.因此,低功耗SoC的驱动电压可从65nm工艺时的1.2V降至0.9V以下。

本文引用地址:https://www.eepw.com.cn/article/190733.htm降低SRAM的电压是SoC实现微细化时存在的最大技术课题之一。SRAM由于集成尺寸比逻辑部分小的晶体管,因此容易导致每个晶体管的阈值电压不均。而且,使6个晶体管联动可实现存储器功能,因此每个晶体管的不均都容易引发性能不良。所以,尖端SoC“需要以较高的成品率制造大容量且低电压工作的SRAM的技术”(东芝半导体系统LSI业务部系统LSI元件技术开发部部长亲松尚人)。

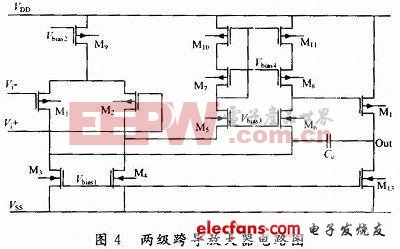

此次,作为满足该要求的混载SRAM技术,东芝开发出了不易受NBTI(negative bias temperatureinstability)等导致的阈值电压变化影响的晶体管技术。NBTI是指晶体管的阈值电压随着时间的推移,受印加电压及温度的影响发生变化的现象。该公司此次的技术由2个要素构成,分别是(1)控制NBTI发生,(2)控制NBTI等导致的阈值电压变动对晶体管工作造成的影响。

在确保95%以上成品率的情况下,SRAM的驱动电压可降至0.9V

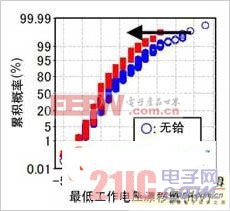

通过向栅极绝缘膜添加Hf,控制NBTI

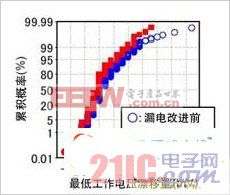

通过改进硅化工艺,控制结漏导致的阈值电压漂移

评论