一种用于FPGA互联资源测试的新方法

摘要:以基于静态随机存储器(SRAM)的现场可编程门阵列(FPGA)为例,在传统的三次测试方法的基础上提出了一种新颖的针对FPGA互联资源的测试方法。该方法运用了层次化的思想,根据开关矩阵中可编程互联点(PIP)两端连线资源的区别将互联资源进行层次化分类,使得以这种方式划分的不同类别的互联资源能够按一定方式进行叠加测试,这就从根本上减少了实际需要的测试配置图形和最小配置次数。最后,文章将文中的测试方法与传统的测试方法在最小配置次数、故障覆盖率等方面进行了一个简单的比较。

关键词:现场可编程门阵列;静态随机存储器;可编程互联点;测试配置图形;故障覆盖率

FPGA (现场可编程门阵列)作为一种可编程的逻辑器件,以其丰富的逻辑资源和极其灵活的可编程特性越来越受到广大用户的青睐。然而,随着工艺水平的发展和实际应用的需要,FPGA的逻辑门数量已从最初的几千门增加到现在的几千万门,与此同时,FPGA内部资源的复杂度也呈几何级数增长。这势必给FPGA的测试工作带来极大的挑战。如何在有限的时间内完成对整个FPGA的可靠性测试而达到尽可能高的故障覆盖率,已经成为每一个测试工作者迫切需要解决的问题。针对FPCA的测试非常复杂,因为FPGA内部具有大量的逻辑资源和布线资源,在用户使用之前,FPGA的功能是不确定的,用户可以根据自己的需求把FPGA配置成某种特定的逻辑,还可以根据需要反复编程,但其中大部分的资源仍处于闲置状态,这就导致针对FPGA的测试不可能像针对ASIC的测试那样对FPGA能够实现的所有功能进行的穷举性测试。在FPGA中,互联资源相当复杂,对于最新的FPGA器件,80%以上的晶体管都包含在互联资源中,所以对FPCA互联资源的测试成了整个测试工作的核心,为此,本文将专注于FPGA互联资源的测试。

1 FPGA的结构与互联资源的故障模型

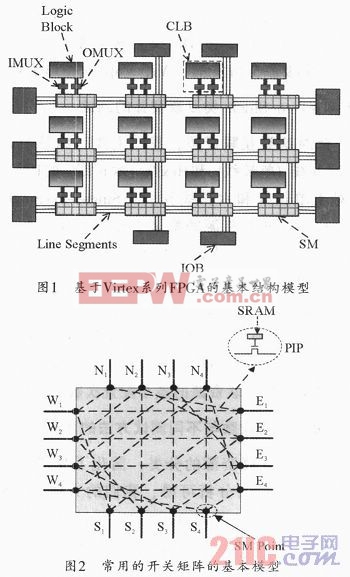

FPGA一般由三种可编程电路和一个可用于存储配置数据的SRAM组成,这三种可编程电路分别是:可编程逻辑块CLB(Configurable Logic Block),输入/输出模块IOB (I/O Block)和互联资源IR(Interconnect Resource)。以xilinx公司的Virtex系列FPGA为例,其结构的基本模型如图1所示,该模型是由可编程逻辑块和开关矩阵组成的二维阵列,在每个CLB内部,逻辑模块通过输入输出多路选择器(I/O MUX)与开关矩阵(SM)相连,开关矩阵同时又为FPGA阵列中不同的CLB之间提供水平和垂直的布线通道。根据布线资源跨越CLB个数的不同,我们将其分为三类:单长线(连接相邻开关矩阵,不跨越任何的CLB的布线),六长线(通过一个开关矩阵跨越五个CLB与另一个开关矩阵相连的布线)和全局长线(贯穿整个FPGA的CLB阵列,具有最小延时的布线)。在每个开关矩阵的内部都具有大量的可编程互联点PIPs (programmable interconnec tpoints),每一个可编程互联点都是一个由可编程的SRAM单元控制的传输门晶体管,图2是一个常用的开关矩阵的基本模型,在开关矩阵的每一个边都有四个连接点,每个连接点都可以通过开关矩阵内部的PIP与其它三边相连接,其中虚线代表了所有可能的连接方式,我们可以通过向SRAM加载配置数据的方式来控制PIP传输门晶体管的通断,当向SRAM单元中写“1”的时候传输管导通,相应的连接建立;当向SRAM单元写“0”的时候传输管断开,相应的连接也就随之断开。

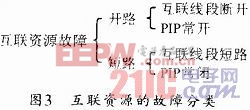

在FPGA里面,互联资源的故障大慨可以分为两类:一类是开路故障,一类是短路故障。开路故障又可以分为PIP的常开故障(PIP开关处于永久性的断开状态)和互联线段的断开故障,而短路故障通常由PIP的常闭故障(PIP开关处于永久性的导通状态)和互联线段短路故障组成。另外,我们将互联资源的固定型故障(固定“1”或固定“0”故障)看成是互连线与电源Vcc和地Vdd的短路故障,而不单独加以考虑。如图3所示,显示了互联资源故障模型的基本分类。

评论