基于FPGA的数字选频器设计

摘要:提出了一种基于FPGA的数字选频器设计方案,该数字选频器应用于八通道的GSM系统直放站,采用低成本的FPGA芯片Xilink Spartan-3A DSP XC3SD3400A进行数字信号处理。给出了较详细的硬件设计方案,并通过Agilent Technologies N5230A网络分析仪对数字选频器进行了测量,被选出的有效相邻信道之间的最小间隔能达到1MHz,能够实现较好的选频功能,可满足实际应用的要求。

关键词:FPGA;数字选频器;GSM;直放站

0 引言

随着移动通信的迅速发展,无论何种无线通信的覆盖区域都将产生弱信号区和盲区,要架设模拟或数字基站成本太高,基础设施也比较复杂,为此提供一种成本低、架设简单,却具有小型基站功能的直放站是很有必要的。GSM移动通信系统在我国经过多年的发展,目前已经拥有最大的网络覆盖规模、最多的用户数、种类多样的业务,在我国移动通信市场中占有重要的地位。本文对GSM直放站的数字无线选频器进行设计,以达到低成本扩大无线网络覆盖范围和优化网络的目的。

1 系统总体结构

GSM900中上下行信道各120个,带宽为24 MHz,其中上行频段为885~909 MHz,下行频段为930~954 MHz,数字选频器工作效果示意图如图1所示。

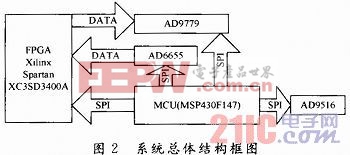

如图1所示,数字选频器就是仅放大选中的频段,抑制未选中的频段,实现降低信道间干扰的目的。系统总体结构框图如图2所示。数字选频系统主要由A/D模块、FPGA可编程逻辑器件模块、D/A模块以及MCU管理模块四部分组成。

软件无线电的思想是将无线电收发信机的数字化点(A/D/A)尽可能靠近天线,理想的情况是在天线的后端进行射频采样,数字化之后,所有的处理都可以用很灵活的方法实现。但是由于目前ADC器件性能的限制,还无法达到在射频端进行数字化,在中频实现数字化是一个较妥的方案。

GSM直放站数字选频系统就是利用数字处理的手段实现滤波器功能,以替代现有直放站中的模拟选频模块。本系统通过AD6655接收下变频后的模拟中频信号,通过A/D采样将模拟信号转换为数字信号,采样频率为122.88 MHz。然后由FPGA按预定算法对来自AD6655的数字信号进行数字处理,处理后的结果再由AD9779转换成模拟信号。MCU通过SPI接口对AD6655,AD9779和AD9516的寄存器进行配置,并与FPGA之间进行通信。

评论