基于CPLD的多DSP及FPGA远程加载设计

摘要:介绍了一种以CPLD为基础的对多DSP和FPCA芯片实现程序远程更新、加载的设计方法。详细分析了软硬件架构及具体实施方案,对以DSP+FPCA为架构的信号处理模块实现远程更新、加载,有重要的使用价值。

关键词:远程加载;CPLD;FPGA器件;DSP

随着硬件技术的大力发展和加工丁艺技术的不断提升,芯片技术日益成熟,软件无线电技术得到广泛应用和迅猛发展。无线电系统在整体体系结构上发生了重大变化,正沿着综合化、模块化、通用化和智能化的方向快速推进。无线电系统将模块化、标准化的硬件构成基本平台,通过软件加载技术来实现尽可能多的功能,为多种信号的功能综合和互联互通提供了技术保障。随着模块应用灵活性要求的不断增加,软件维护及升级需求的日益迫切,给软件加载技术提出了更高要求。本文提出了一种基于CPLD的多处理器远程加载管理设计应用方案,系统实现了从远端下发命令字和更新数据即可完成模块的程序更新升级和重新加载,实现软件维护和模块功能切换,满足日益复杂的系统使用要求。

1 数字处理模块

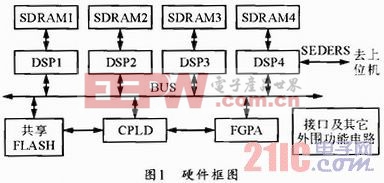

数字处理模块主要完成基带信号调制解调、RS编解码算法实现、收发通道实时控制、导航算法实现、信息层的协议实现以及大量的数据融合算法实现等。硬件设计采用了FPGA+DSP的设计构架,以1颗Altera公司的Stratix系列FPGA和4颗TI公司的DSP作为设计核心完成以上功能实现,框图如图1所示。系统要求数字处理模块要适应系统通用化和智能化的设计要求,具备远程自动更新升级、加载等功能,为系统功能多样化、维护简易化打下基础。根据系统要求和模块设计实际,结合CPLD芯片稳定性高、设计灵活的自身特点,确定采用CPLD作为整个数字处理模块的功能管理芯片,实现对整个处理模块的电源管理、状态检测、上电复位管理、各DSP及FPGA的程序加载管理、远程更新等功能处理。

当系统需要对本模块的软件进行升级或者模块功能重构时,系统将更新命令字和更新内容通过SEDERS总线下发至DSP4,再送入CPLD进行解码、识别分类,根据指令要求启动CPLD对FLASH中的相应空间进行擦除、更新操作。当操作完成后,CPLD强行启动DSP或FPCA,重新加载FLASH中的程序,完成系统软件升级或者模块功能重构任务。

评论