星载环境FPGA软件在轨重加载的一种方法

摘要:FPGA在空间系统中已经广泛应用,为了满足系统可靠性和可扩展性的要求,实现FPGA软件的在轨重加载迫在眉睫。根据FPGA的加载配置原理,以Xilinx公司的Virtex-Ⅱ系列FPGA为实例,介绍了FPGA在轨重加载的硬件电路设计以及软件设计。经过实验室测试验证,该设计方法合理可行,满足星载环境下FPGA软件在轨编程及重加载的设计需求。

关键词:FPGA;在轨重加载;在轨编程;星载环境

0 引言

FPGA已经广泛应用于星载信号处理系统中,然而其在空间环境中的可靠性设计是一个难题。一方面,FPGA软件可能受到外部空间环境影响而产生各种问题,特别是单粒子效应造成的FPGA程序出错,其导致的后果是严重的甚至是灾难性的;另一方面,当FPGA软件本身存在设计缺陷或者由于卫星系统改变应用需求时,若能实现星载环境下FPGA软件的远程更新升级,其软件系统的生命周期便可以得到延长,同时产生的经济效益也是不可估量的。

为此,本文介绍一种星载环境下FPGA软件在轨重加载的方法,通过星上系统的1553B接口接收FPGA配置数据文件,在DSP和CPLD的控制下,灵活地实现FPGA程序的在轨编程及重加载。

1 FPGA加载原理

基于SRAM工艺的FPGA由于在掉电后配置数据丢失,因此需要在上电后对其进行加载,而配置数据被保存在外部的非易失存储器中。

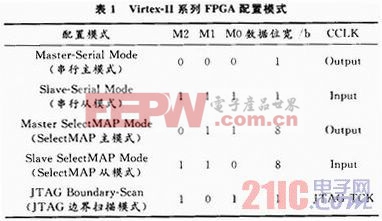

Xilinx公司的Virtex-Ⅱ系列FPGA通过芯片配置管脚MODE PIN(M0,M1,M2),可以实现5种配置模式,详见表1。

上述5种模式中,JTAG边界扫描模式具有最高的优先级,其加载方式是通过专用JTAG口对FPGA进行访问。SelectMAP模式实际上就是并行模式,其加载时的数据访问位宽为8 b,加载过程与串行模式相同。主模式和从模式的区别在于时钟是由FPGA自身提供,亦或是外部提供,当FPGA主动输出时钟时即为主模式,反之即为从模式。

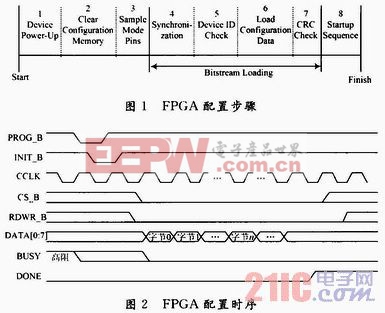

FPGA的配置过程如图1所示,主要由3个阶段8个步骤组成。FPGA在Slave SelectMAP模式下配置过程中使用的信号包括:PROG_B,INIT_ B,CCLK,CS_B,RDWR_B,DATA[0:7],BUSY,DONE,其时序关系如图2所示。

根据图1和图2,Slave SelelctMAP模式下,FPGA加载过程描述如下:

第1阶段:启动和初始化,分为3个步骤:

FPGA上电正常后,通过PROG_B引脚低脉冲进行FPGA异步复位,使得FPGA内部逻辑清零;PROG_B拉高后,停止外部复位,INIT_B引脚会在自动产生一个由低到高的跳变,指示FPGA内部初始化完成,可以进行数据下载;FPGA检测其专用的配置模式管脚M0~M2的电平,从而确定加载模式。

第2阶段:比特流加载,分为4个步骤。INIT_B信号变高后,不需要额外的等待时间,Virtex器件就可以立即开始数据的配置。比特流数据在外部CCLK信号上升沿按字节方式置入。其中的Synchronization(同步)、Device ID Check(检测器件ID号和配置数据中的ID号是否匹配)、Load Configuration Data(下载数据流)和CRCCheck(CRC校验)对用户是完全透明的,同步字、配置数据中ID号和CRC校验和都是在生成配置数据文件时和配置数据一起打包,嵌入在配置数据文件当中。

第3阶段:Startup启动。在成功校验CRC码位后,FPGA进入Startup状态。它是由8相状态机实现的,中间包括等待DCM锁相、DCI匹配等几个状态,最后FPGA释放外部DONE引脚,对外输出高阻态,由外部上拉高,指示FPGA加载成功。

评论