一种基于FPGA的多电平变流器脉冲生成方法

摘要:提出一种基于现场可编程门阵列(FPGA)及不对称规则采样的级联H桥型变流器触发脉冲的快速生成方法。详细分析了基于不对称规则采样的载波相移SPWM(CPS-SPWM)触发脉冲的快速生成原理。重点介绍了基于FPGA的CPS-SPWM触发脉冲快速生成的实现方法。理论分析和实验结果表明,在既没有增加采样频率,又没有增加计算量的情况下,相对基于对称规则采样的CPS-SPWM脉冲生成方法,该方法具有较快的生成速度,并可广泛应用于DSTATCOM等高压级联H桥多电平变流器触发脉冲的快速生成。

关键词:变流器;不对称规则采样;脉冲生成

1 引言

CPS-SPWM技术由于具有等效开关频率高、输出电压谐波含量小、信号传输带宽较宽及控制方法简单等优良特性而被广泛应用在级联H桥多电平变流器中。

较典型的SPWM实现方法主要分为两类:自然采样法和规则采样法,而规则采样法通常存在对称规则采样和不对称规则采样两种方法。文献提出基于不对称规则采样法的GPS-SPWM实现方法,其结论为:相对于规则采样法,采样点和计算量增加了一倍;但变流器输出电压谐波含量却大为减少,波形的不对称性也有所改善。

在此阐述了级联H桥多电平变流器的CPS-PWM脉冲生成时序。在此基础上,提出一种应用于级联H桥多电平变流器,基于不对称规则采样的CPS-SPWM触发脉冲的快速、精确的生成方法。介绍了基于FPGA的级联H桥多电平变流器的CPS-PWM触发脉冲快速生成的实现方法。

2 CPS-SPWM触发脉冲的生成时序

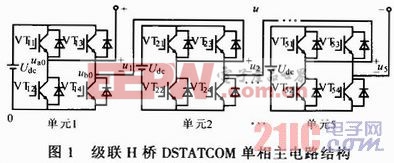

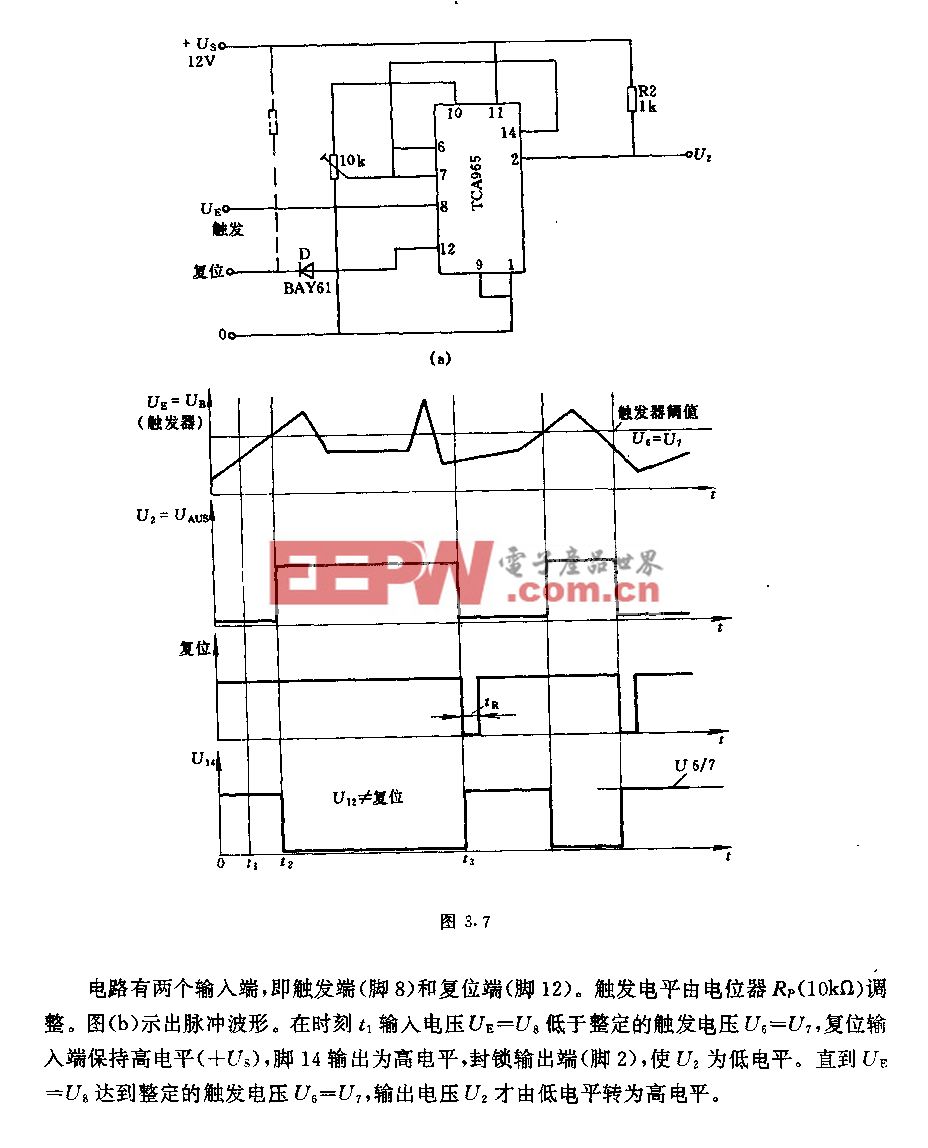

级联H桥型多电平变流器的单相主电路结构如图1所示,为分析方便,取级联单元数N=5。元左、右桥臂上、下IGBT开关器件;ux为各单元交流侧输出电压;u为级联装置单相输出总电压;Udc为各单元直流侧电压。装置采用基于CPS-SPWM的单极性开关调制方法,各单元载波urx相互错开时间Ts=Tc/(2N),其中Tc为载波周期。

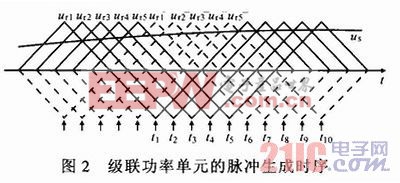

各单元的脉冲生成时序如图2所示。urx的相位与urx-相差180°,分别用来形成功率单元x的VTx1和VTx4的触发脉冲;us为SPWM调制波。

如图所示,在tn时刻(n=1,…,10;Ts为一个采样周期,tk+1-tk=Ts)采样调制波us,根据不同的采样方法,依次生成SPWM触发脉冲Px1,Px4,分别对应触发VTx1和VTx4;VTx2,VTx3的触发脉冲Px2,Px3分别与Px1,Px4相反,实际应用中加死区延时。

实际应用中,载波并不以具体波形存在,而代之以双向计数器。这里定义计数器Tx1和Tx4分别对应载波urx和urx-;另设Tx1CMP和Tx4CMP分别为Tx1和Tx4的比较寄存器。

3 CPS-SPWM触发脉冲快速生成原理

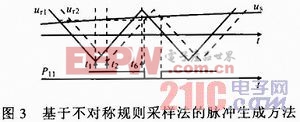

不对称规则采样方法是指在一个载波周期中的峰、谷各采样一次调制波,如图3所示。在t1时刻采样us,计算占空比并加载至T11CMP,在t2时刻T11开始增计数,当比较匹配时形成P11的下降沿;在t6时刻再次采样us,计算占空比并更新T11CMP,在T11上溢时刻开始减计数,当比较匹配时形成P11下一个脉冲的上升沿。

可见,依据此种方法生成的触发脉冲,较理论上的脉冲延时亦仅为一个Ts,且由于在一个载波周期中两次采样正弦调制波,精度较高。该方法主要缺点是提高了采样频率,增加了计算工作量。但对于如图2所示的级联功率单元的触发时序而言,该方法既没有提高采样频率,又没有增加计算量,具体分析如下:

根据图3,对于生成同一个触发脉冲,如P11,分别在t1和t6时刻都进行了采样,脉冲生成的采样频率比对称规则采样法高出了1倍。但实际上,参照图2所示的级联单元脉冲生成时序,t6时刻也对应触发脉冲P14生成的采样时刻,因此,总体而言,采样频率没有提高,只是同一采样时刻要进行两个占空比值的计算,如t6时刻,分别要计算P14,P11的占空比D14,D11。只要证明此时D14等于D11即可说明该方法无需增加计算量,证明如下:设TW11=D11Tc,TW14=D14Tc,显然存在:(Tc-TW11)/2=(Tc-TW14)/2,解得TW11=TW14,也即D11=D14,由此可知,任何采样时刻仅需进行一次占空比计算,而无需增加额外的计算量。

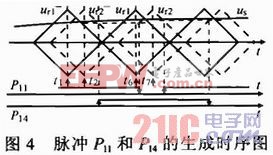

P11和P14生成过程及时序为如图4所示。在t1时刻,采样us并计算D11(D14),并加载到T11CMP和T14CMP,当下一个同步信号到达即t2时刻清零T11开始增计数,生成P11的下降沿;同时,重载T14并开始减计数,生成P14的上升沿。同理,在t6时刻,采样us计算D14(D11),并加载到T14CMP和T11CMP,在t7时刻分别清零T14开始增计数,重载T11并开始减计数,生成P14的下降沿和P11的上升沿。

参照图2,整个级联单元的脉冲生成时序为:

①t1,t2,t3,t4,t5时刻采样依次生成的SPWM触发脉冲为:P11↓(下降沿)和P14↑(上升沿),P21↓和P24↑,P31↓和P34↑,P41↓和P44↑,P51↓和P54↑;

②t6,t7,t8,t9,t10时刻采样依次生成的SPWM触发脉冲为:P14↓和P11↑,P24↓和P21↑,P34↓和P31↑,P44↓和P41↑,P54↓和P51↑。

4 触发脉冲快速生成的实现方法

为充分发挥上述级联H桥变流器CPS-SPWM触发脉冲快速生成方法的优越性,采用规模大、集成度高、可靠性强、编程灵活的FPGA芯片EP2C20/EP2C5,来完成触发脉冲生成及其他包括分配、传输、驱动、逻辑综合与控制等功能。

实际工程中,触发脉冲生成由两部分组成,即顶层触发监控模块、底层脉冲生成模块,两模块之间采用光纤通讯模式,具体阐述如下:

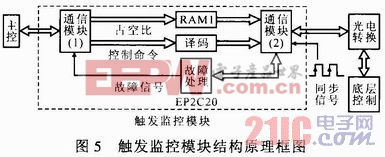

(1)顶层触发监控模块 触发监控模块主要负责触发脉冲占空比、同步信号、控制命令、底层控制参数等信息的下发;采集处理底层控制系统的功率单元运行状态以及逻辑综合、故障处理等任务,控制结构原理如图5所示。

通信模块(2)是整个触发监控系统中的关键性环节,主要承担的任务有:①接收模块(1)的译码控制命令,判断命令类型;②同步信号的编码、下发;③接收底层控制系统上传的各功率单元运行状态信息,存储到RAM2相应存储单元中并传输到故障处理模块;接收故障模块向底层控制系统发出的故障处理命令。

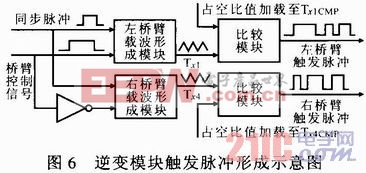

(2)底层脉冲生成模块 底层脉冲生成模块除负责脉冲生成、驱动控制任务外,还担负着整个功率单元的通信和故障处理任务。该模块主要由脉冲生成单元、通信单元及IPM驱动接口电路等几部分组成。脉冲形成单元负责CPS-SPWM触发脉冲的生成任务。脉冲生成的原理在前文中已经作了详细的介绍,这里将重点介绍各功率单元的底层控制系统脉冲生成的过程,如图6所示。

脉冲形成单元主要由载波形成模块和比较模块两大部分组成:载波形成模块用来形成三角载波。比较模块的主要任务是生成IGBT触发脉冲。即将存放在Tx1CMP/Tx4CMP中的占空比数据与Tx1/TX4中的载波数据进行比较,输出PWM触发脉冲。需要说明的是,Tx1CMP/Tx4CMP中的数据在对Tx1/Tx4进行清零或重载的同时,进行数据更新(重载)。

5 实验

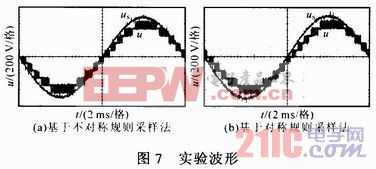

实验模型参照图1,直流侧电压Udc=90 V,载波频率1/Tc=1.28 kHz,采样周期Ts=78.125μs。脉冲传输采用编码方式,传输延时Ttr≈5μs。实验波形如图7所示。

图7a,b分别为基于对称和不对称规则采样法的输出电压u及调制波us的波形。可见,基于对称规则采样法的u滞后us约5 ms;而基于不对称规则采样法的u滞后us约3 ms,具有较快的生成速度。

6 结论

理论分析和实验结果表明:此处所述基于不对称规则采样法的CPS-SPWM脉冲生成方法,相对基于对称规则采样法的CPS-SPWM脉冲生成方法,既没有增加采样频率,也没有增加计算工作量,具有较快的生成速度。此外,由于采用了基于FPGA的CPS-SPWM脉冲生成的实现方法,为上述CPS-SPWM脉冲的快速生成提供了重要保障。

评论