基于FPGA的IRIG-B编码器的设计

我国靶场测量、工业控制、电力系统测量与保护、计算、通信、气象等测试设备均采用国际标准IRIG-B格式的时间码(简称B码)作为时间同步标准。B码是一种串行的时间格式,分为直流码(DC码)和交流码(AC码)两种,其格式和码元定时在文献[1]中有详细描述。本文介绍一种基于FPGA并执行IRIG-B标准的AC/DC编码技术,与基于MCU或者DSP和数字逻辑电路实现的编码方法相比,该技术可以大大降低系统的设计难度,降低成本,提高B码的精确性和系统灵活性。

本文引用地址:https://www.eepw.com.cn/article/189993.htm在此,组合GPS引擎和FPGA,得到B码的编码输出,直接采用GPS引擎的100 pps信号触发输出B码的每个码元,利用从100 pps中恢复的1 pps信号提供B码的时间参考点。DC编码和AC数字调制均由纯硬件逻辑通过查找表实现,它能使每个码元的上升沿都非常精准,都可以作为百分秒的时间参考点,而计时链的预进位功能则保证了绝对时间的精确,不仅可以满足实时系统对时间同步,还可以实现多节点的数据采集严格同步,为分析和度量异步发生的事件提供有方的支持。

1 IRIG-B编码格式

IRIG标准规定的B格式码如图1所示,每秒钟发1次,每次100个码元,包含1个同步参考点(Pr脉冲的上升沿)和10个索引标记。码元宽度为10 ms,用高电平宽度为8 ms的脉冲表示索引标记,用宽度为5 ms的脉冲表示逻辑1,用宽度为2:ms的脉冲表示逻辑0。

如图1所示,交流码的载波是1 kHz正弦信号,幅度变化峰一峰值范围为0.5~10 V。调制比为U1/U0=1/6~1/2,即逻辑1是5个幅度为U1的1 kHz正弦信号,逻辑0是2个幅度为U1的1 kHz正弦信号,索引标记是8个幅度为U1的1 kHz正弦信号,其他时间是幅度为U0的1 kHz正弦信号。

2 系统方案

2.1 系统原理框图

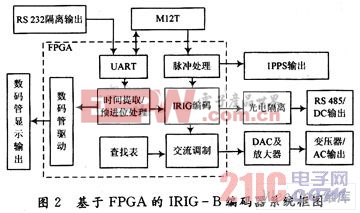

设计授时系统需要一个精准时基。在此利用精密授时型GPS引擎M12T作为系统时基,利用AlteraFPGA检测M12T输出的百分秒(100 pps)同步信号和经串口输出的绝对时间信号,编码后输出到DC/AC接口模块,再输出到物理链路,系统结构图如图2所示。

上述系统首先实现了B码直流编码,而后在直流码的基础上实现交流调制,以得到交流码,同时提供恢复每秒脉冲数输出和隔离RS 232串行口输出且符合Motorola格式的时间码,以及数码管的时间显示。时间显示部分用FPGA实现比较简单,下文不再详述。

评论