基于FPGA的数字三相锁相环优化设计

摘要:数字三相锁相环中含有大量乘法运算和三角函数运算,占用大量的硬件逻辑资源。为此,提出一种数字三相锁相环的优化实现方案,利用乘法模块复用和CORDIC算法实现三角函数运算,并用Vetilog HDL硬件描述语言对优化前后的算法进行了编码实现。仿真和实验结果表明,优化后的数字三相锁相环大大节省了FPGA的资源,并能快速、准确地锁定相位,具有良好的性能。

关键词:FPGA;三相锁相环;乘法复用;CORDIC

0 引言

在PWM整流器、不间断电源(UPS)、有源电力滤波器(APF)等需要并网的电力电子装置控制中,获得电网电压的相位是系统控制的前提。一般都采用锁相环PLL来获取电网电压的相位。三相电网电压可能存在三相不平衡,电压有谐波、频率、相位突变。为了全面反映电网电压的真实状况,采用三相锁相环来锁定电网电压相位角,而且三相锁相环的抗干扰能力更强。采用现场可编程门阵列(FPGA),并以硬件方式实现三相锁相环,可充分体现FPGA硬件的高速性,且不受CPU资源的制约。

本文对数字三相锁相环的系统原理和算法实现进行了研究,并对三相锁相环在FPGA中实现的算法进行了优化设计。通过采用乘法模块复用和基于坐标旋转数字式计算机(CORDIC)的算法计算含有三角函数的坐标转换模块,节省了数字三相锁相环实现所需的硬件开销。用硬件描述语言Verilog HDL设计出了整个三相锁相环系统。该三相锁相环在以Altera公司芯片CyconeⅡEP2C15AF256C8为主芯片的实验板上进行了验证。

1 三相锁相环的基本原理

1.1 锁相环基本原理

锁相环一般由鉴相器(PD)、环路滤波器(LF)、压控振荡器(VCO)组成。锁相环是一个相位反馈系统。鉴相器把周期性的输入信号与VCO反馈来的相位信号进行比较,得到一个相位误差;误差经环路滤波器进行滤波,环路滤波器的输出被用作控制信号送入VCO,用来消除输入、输出信号的相位差。

1.2 三相锁相环的结构与原理

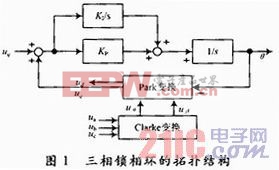

三相锁相环的拓扑结构如图1所示。

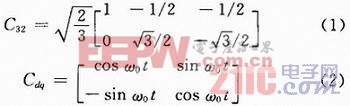

数字三相锁相环的关键模块是矢量控制中的2个系统变换:从a-b-c三相静止坐标到α-β两相静止坐标的Clarke变换(C32)和从α-β两相静止坐标到d-q两相旋转坐标(基波同步速为ω0)的Park变换(Cdq):

fpga相关文章:fpga是什么

锁相环相关文章:锁相环原理

评论