基于IP核的FPGA 设计方法

几年前设计专用集成电路(ASIC) 还是少数集成电路设计工程师的事, 随着硅的集成度不断提高,百万门的ASIC 已不难实现, 系统制造公司的设计人员正越来越多地采用ASIC 技术集成系统级功能(System L evel In tegrete - SL I) , 或称片上系统(System on a ch ip ) , 但ASIC 设计能力跟不上制造能力的矛盾也日益突出。现在设计人员已不必全部用逻辑门去设计ASIC, 类似于用集成电路( IC) 芯片在印制板上的设计,ASIC 设计人员可以应用等效于印制板上IC 芯片的功能模块, 称为核(core)、或知识产权( IP) 宏单元进行系统设计, 这就是基于核的设计方法。CPU、存储器、总线控制器、接口电路、DSP 等都可成为核。但是ASIC 设计与印制板(PCB) 设计有很大区别,ASIC 必须用EDA 工具进行硬件设计, 主要问题都是通过计算机仿真解决, 而不能象印制板设计那样通过实验调试解决, 另外ASIC 的制造还需要数量可观(一般数万美元) 的不可重复工程费用(NRE)。80年代后期出现的现场可编程门阵列(FPGA ) 和复杂可编程逻辑器件(CPLD) 是ASIC 的一种, 其优点是在制造厂家提供的FPGA 或CPLD 芯片上, 可由设计工程师对其进行现场编程完成ASIC 的最后设计, 而不需昂贵的NRE 费。现在FPGA 的规模已达到百万门, 如XILINX 公司的V irtex 系列, 完全可以实现片上系统,其设计方法将逐步转向核基设计。

本文引用地址:https://www.eepw.com.cn/article/189793.htm1 核的分类和特点

核是一种预定义的并经过验证的复杂功能模块, 它可以集成到系统设计中。核基设计主要特点是可重复使用已有设计模块, 缩短设计时间, 减少设计风险, 通过高层的集成可望提高整个系统的性能。在FPGA 设计中的核分为三种, 如表1所示:

表1 核的分类和特点

硬核

(hard core)

预定义的已布局布线的模块 不能修改设计, 必须采指定实现技术 时序性能有保证

固核

(firm core) HDL 源码,与实现技术有关的网表 部分功能可以修改, 采用指定的实现技术 关键路径时序可控制

软件

(soft core)

行为级或RTL 级HDL源码 可修改设计,与具体实现技术无关 时序性能无保证, 由使用者确定

硬核是针对特定的实现技术优化的, 它具有不能修改的结构和布局布线, 可作为库元件使用, 且时序性能稳定, 但硬核不能按设计需要修改和调整时序。固核由HDL 源码和与实现技术有关的网表组成, 使用者可按规定增减部分功能。固核的关键路径时序是固定的, 但其实现技术不能更改, 即不同厂家FPGA 的固核不能互换使用。软核是可综合的硬件描述语言(HDL ) 源码, 它与实现技术无关, 可按使用者需要修改, 具有最大的使用灵活性, 但软核的关键路径时序性能无保证, 最终性能主要决定于使用者采用的综合、布局布线和实现技术。

在FPGA 设计中, 由于不同厂家的具体实现技术差别较大, 完全与硬件实现技术无关的软核性能受到很大限制, 而硬核缺少使用的灵活性, 因此作为软、硬核折中的固核使用较多。以上是具有代表性的核的分类, 在实际使用中, 某种功能的核往往以各种形式出现, 由使用者按需要选用, 软核也不仅只有HDL 源码, 还包括用于功能测试的行为模型和测试向量, 用于指导综合的约束文件。

2 核基FPGA 设计方法简介

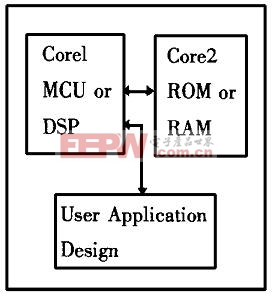

在核基设计中, 一个完整的设计主要由两部分组成, 一部分是核, 如图1中的MCU、RAM , 另一部分是用户自己定义的逻辑电路。按系统设计的要求将这些功能模块连接在一起就完成了芯片的设计,各个核或功能块的连接目前还没有统一的标准, 因不同的设计而定, 一般应满足一定的时序要求。作为核基设计的第一步是选择合适的核, 这主要从核的功能、性能可靠性和实现技术几方面来选择。

图1 核基设计芯片示意图

fpga相关文章:fpga是什么

评论