FPGA远程更新重启系统

正文

本文引用地址:https://www.eepw.com.cn/article/189787.htm1) 因为FPGA具有开发周期短,可更新等优点,现在有越来越多的通讯系统采用FPGA作为实际产品方案。已经有大量的FPGA应用到通讯系统中,为了降低系统维护的人力成本,需要能够实现FPGA远程版本更新。本文将以Xilinx Virtex6 为例描述如何实现远程FPGA版本更新/重启。

2) FPGA加载主要分为2大类,一类是主动模式(master)另一类是从模式(slave).在主动模式时FPGA会外挂存储器存储FPGA bit映像,FPGA会主动提供时钟访问外部存储器。在从模式时,FPGA作为从设备被挂在控制器CPU上由处理器控制对FPGA编程。上述两种模式中,因为从模式FPGA由外部CPU控制编程,可以通过远程更新CPU文件就可以实现对FPGA的版本更新,非常方便。但是当CPU外挂的FPGA较多时会使系统加载时间过长,降低系统启动速度。这里将利用FPGA 多重启(multi-boot)功能实现在主动模式下版本更新。

3) 远程更新流程

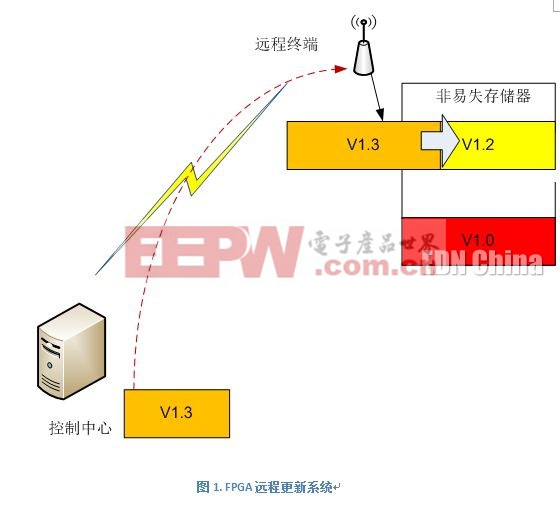

当系统需要升级时,中心控制系统需要将新的FPGA比特映像文件直接发布到远程子系统,由远程 子系统将比特文件更新到非易失存储器。然后由FPGA内部控制逻辑重新启动。比特映像文件更新后,下次上电启动将从新的比特映像文件。

如图 1. FPGA远程更新系统

多重启动 FPGA 介绍

评论