基于FPGA的多功能数字钟设计

摘要:文中简要介绍了一种基于FPGA的多功能数字钟设计方案。在实现数字钟计时、校时和整点报时等基本功能的基础上增加世界时钟功能,能够将北京时间快速转换为格林威治标准时。该方案采用VHDL和原理图相结合的设计输入方式,在QuartusⅡ开发环境下完成设计、编译和仿真,并在FPGA硬件开发板上进行测试,实验证明该设计方案切实可行,对FPGA的应用和数字钟的设计具有一定参考价值。

关键词:FPGA;VHDL;数字钟;世界时钟;QuartusⅡ

现场可编程门阵列(Field Programmable Gate Arrays,FPGA)是一种可编程使用的信号处理器件。通过改变配置信息,用户可对其功能进行定义,以满足设计需求。通过开发,FPGA能够实现任何数字器件的功能。与传统数字电路相比,FPGA具有可编程、高集成度、高可靠性和高速等优点。

1 数字钟总体设计

本文以FPGA平台为基础,在QuartusⅡ开发环境下设计开发多功能数字钟。数字钟实现的功能如下:

1)计时功能:进行正常的时、分、秒计时,并由6只8段数码管分别显示时、分、秒时间。

2)校时功能:当时校时按键按下时,计时器时位迅速增加,并按24小时循环;当分校时按键按下时,计时器分位迅速增加,并按60分循环。

3)整点报时功能:当计时到达59分53秒时开始报时,在59分53秒、55秒、57秒蜂鸣声频率为512 Hz;到达59分59秒为最后一声报时,蜂鸣声频率为1 kHz。

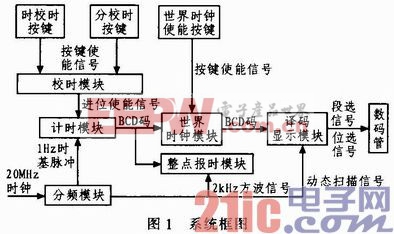

4)世界时钟功能:默认当前显示时间为北京时间(GMT+8),当按下世界时按键时,显示时间将转换为格林威治标准时(GMT)。数字钟电路的模块框图,如图1所示。

2 功能模块的工作原理及设计实现

系统主要由6大模块组成,即分频模块、计时模块、校时模块、译码显示模块、整点报时模块和世界时钟模块。

2.1 分频模块的工作原理及设计实现

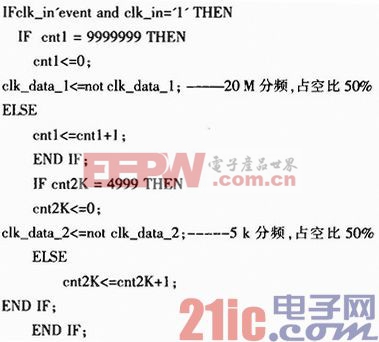

本设计选用的FPGA开发板板载20 MHz有源晶振,为了得到占空比50%的1 Hz时基脉冲及2 kHz方波信号(用于驱动译码显示模块以及为整点报时模块提供不同频率的信号以产生不同音调的声音),需要对板载时钟信号进行分频。分频模块采用VHDL语言实现,对20 MHz时钟信号分别进行两千万和一万分频。具体实现代码如下:

2.2 计时模块和校时模块的工作原理及设计实现

计时模块由60进制秒计数器、60进制分计数器和24进制时计数器级联构成,采用同步时序电路实现。当计数器处于正常计数状态时,3个计数器的时钟信号均为1Hz时基脉冲,秒计数器对1 Hz的时基脉冲进行计数,其进位输出信号cos_in作为分计数器的使能信号,而分计数器的进位输出信号com_in又作为时计数器的使能信号。在计时模块的基础上,数字钟通过增加两个按键分别实现对小时和分钟的调整。这两个按键能够产生时计数器和分计数器的另一路使能信号,即按下时校时按键时,时计数器使能信号持续有效,由于采用同步时序电路,时计数器能够持续增加,达到调整时间的目的。按下分校时按键时原理相同。此外,校时模块还对校时按键进行防抖动处理,提高系统的可靠性和抗干扰能力。

fpga相关文章:fpga是什么

尘埃粒子计数器相关文章:尘埃粒子计数器原理

评论