基于FPGA的相关测速系统

相关测速是以随机过程的相关理论和信息理论为基础发展起来的[1-2],它的应用始于上世纪40年代,首先应用于军事上,然后逐渐转移到科学研究和民用上,现在已经在各个领域内得到日益广泛的应用。

本文引用地址:https://www.eepw.com.cn/article/189729.htm尽管相关测速的运算量非常巨大,但是随着EDA技术的高速发展,大规模可编程逻辑器件CPLD/FPGA的出现,集成电路做得比以前更快、规模更大。设计人员有很大的自由度去设计实现用途专一的集成化数字电路:在实验室里,在电脑系统前,现场设计、现场编程、现场配置、现场修改和现场验证,从而在现场实现数字系统的单片化设计和应用。这意味着无需更改电路,只要改写FPGA内部功能,整个系统即可实现新功能,即一个最小的芯片方案可以转换来执行多个功能,硬件的配置变得如同软件一样灵活方便,而其速度和集成度,也随着VLS工艺的发展而迅速提高,这就为相关测速的实际应用提供了硬件平台。只要找到合适的算法并建立相应的硬件处理系统,运算速度和精度就能达到预期的要求。

1 系统硬件及相关算法的确定

本文测速的原理是:以CCD摄像头作为前端装置,将CCD摄像头所采集的图像信息送到FPGA中,由FPGA对其进行处理,并给出当前运行的速度。在满足速度上限的条件下,连续两次采集的图像必然有重叠的部分。对连续两次的图像进行相关处理,就可以得到它们之间的位置关系,再结合采样间隔时间,从而可以得出速度。

由于图像处理算法涉及的运算量比较大,对系统的快速处理能力和大数据量的吞吐能力有严格的要求[3],因此系统中的核心器件FPGA的选择必须遵循以下原则:(1)调试使用方便;(2)适当的响应速度;(3)适当够用的逻辑资源;(4)足够的输入输出(I/O)端口。

根据系统要求,本文采用Altera公司的超大规模可编程逻辑器件Cyclone II[4]。Cyclone II系列FPGA是继Cyclone系列低成本FPGA在市场上取得成功之后,Altera公司推出的更低成本的FPGA。Altera采用相同的方法在尽可能小的裸片面积上构建了Cyclone II系列,扩展了低成本FPGA的密度,最多达68 416个逻辑单元(LE)和1.1 Mbit的嵌入式存储器,从而可以在低成本的FPGA上实现复杂的数字系统。优异的性价比使CycloneII系列FPGA可以广泛地应用于汽车电子、消费电子、音/视频处理、通信以及测试测量等终端产品市场。

在测速系统的设计中,假设摄像头采集到的原始图大小为1 280×1 024,为了保证采集的图像背景区域能够有明显的目标,比较理想的情况是将模板区域取得越大越好,将目标全部包括在内[5-6]。当搜索区域大小为m×m, 模板大小为n×n时,归一化互相关算法所需的运算次数约为(5n2+9)×(m-n+1)2次,计算量巨大。如果采用512×512大小的搜索区域,模板采用32×32大小,运算乘加次数近12亿次,硬件将无法提供足够的乘加器。如果采用128×128的搜索区域和32×32的模板,图像的检索区域比较小,测速的范围会比较低,精度也会下降。综合考虑摄像头采集图像的范围和精度,并且充分利用硬件所能提供的内部存储单元,本文将搜索区域设定为256×256,模板大小设定为32×32,如图1所示。

2 测速系统的构成及设计

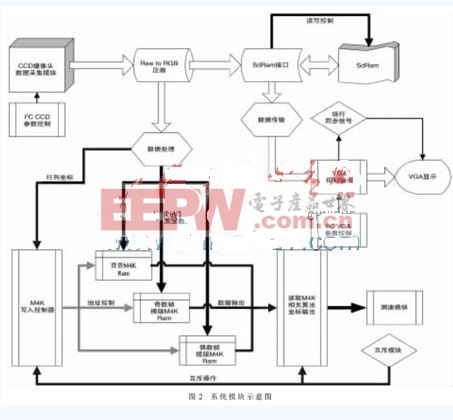

根据所需的功能,将系统划分为以下几个模块,分别加以实现。如图2所示。

(1)CCD摄像头数据采集模块

摄像头采集的数据需要有图像帧和消隐帧。当前帧是图像帧时,读入图像的行数据,读入1 280×1 024个数据后,列计数X_Cont和行计数Y_Cont归零。消隐帧时不输出。

评论