ispPAC及其滤波器设计

ispPAC简介

本文引用地址:https://www.eepw.com.cn/article/189712.htm自1992年美国Lattice公司推出了系统可编程

(In-System Programmabliity)技术,增加了一种与传统数字电子系统不同的设计和实现方法。在1999年底,Lattice公司又推出了系统内可编程模拟电路,又开辟了一种模拟电路设计方法的新思维,为电子设计自动化(EDA)技术开拓了更为广阔的前景。

同数字系统内可编程大规模集成电路(ispLSI)一样,它使设计者用开发软件在计算机中设计、修改,并能进行电路特性模拟,最后通过下载电缆将设计下载至芯片中。

系统内可编程器件可以实现三种基本功能:(1)信号调整;(2)信号处理(3)信号转换。信号调整主要是对信号进行放大、衰减、滤波。信号处理是人才济济对信号进行求和、求差、积分运算。信号转换是把数字信号转换成模拟信号。目前已推出了三种器件:ispPAC10、ispPAC20和ispPAC80。它的开发软件为Lattice公司的PAC-Designer。

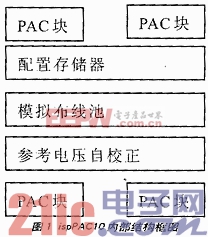

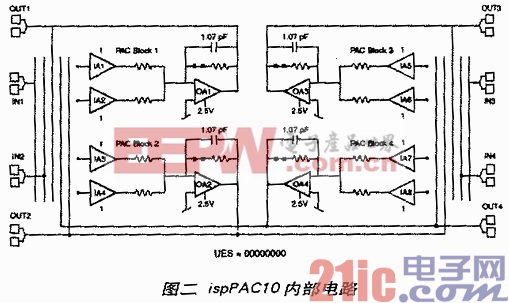

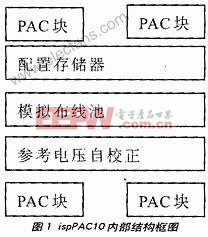

系统内可编程模拟电路具有可模拟信号进行放大、转换、滤波的功能,是通过器件内的多个功能块的互联并能对电路进行重构以达到能调整电路的增益、带宽和阈值。编程次数可达1万次。其内部结构及电路如图1、2所示。

IspPAC10器件的结构由四个基本单元电路(PAC)、模拟布线池、配置存储器、参考电压,自动校正单元和ISP接口所组成。器件用5V单电源供电。基本单元电路称用5V单电源供电。基本单元电路称为PAC块(PAC block),它由两个仪用放大器和一个输出放大器所组成,配以电阻、电容构成一个真正的差分输入/差分输出的基本单元电路,如图2所示。所谓真正的差分输入/差分输出是指每个仪用放大器有两个输入端,

输出放大器的输出也有两个输出端。电路的输入阻抗为10 9,共模抑制比为69dB,增益调整范围不-10~+10倍。PAC块中电路的增益和特性都可以用可编程的方法来改变,器件可配置成1~1万倍的各种增益。输出放大器中的电容CF有128种值可供选择。反馈电阻RF可以断开或连通。器件中的基本单元可以通过模拟布线池(Analog Routing Pool)实现互联,以便实现各 种电路的组合。

每个PAC块都可以独立地构成电路,

也可以采用级联的方式构成电路,以实现复杂的模拟电路功能。例如,各个PAC块作为独立的电路工作,图4(b)为四个PAC块级联构成一个复杂的电路。利用基本单元电路的组合可进行放大、求二阶有源滤波器和和梯型滤波器,且无需在器件外部连接电阻、电容元件。

评论