基于多软件平台协同工作的FIR滤波器设计

摘要:提出了利用多软件平台进行FIR数字滤波器的协同设计,改变了传统的只用硬件电路设计的方法,将整个数字滤波系统的硬件设计趋于软件化,采用Lattice公司的可编程模拟器件ispPAC20和Altera公司的FPGA设计架构整个FIR滤波器实验系统。由于ispPAC20和FPGA器件的高度集成化以及结构的可重构、可编程,使开发人员随时可重复配置满足各种性能要求的滤波器系统,将整个系统变得更小型化、更易于升级维护且更灵活。

关键词:FIR数字滤波器;FPGA;ispPAC20

0 引言

1992年美国Lattice公司发明了在系统可编程技术,彻底改变了传统数字电子技术系统的设计和实现方法,开创了数字系统设计的革命性时代。在1999年,Lattice公司又推出了在系统可编程模拟电路,为电子设计自动化技术的应用开拓了更为广阔的前景。

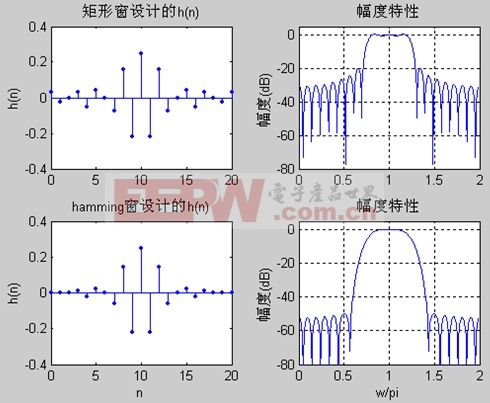

随着信息科学和计算机技术的迅速发展,数字信号处理在20世纪末期得到了飞跃式的发展。在数字信号处理中数字滤波是重要的环节,经典数字滤波器从实现的网络结构或者单脉冲响应长度分类,主要分为有限脉冲响应(FIR)和无限脉冲响应(IIR)两大类;与HR滤波器相比FIR滤波器的计算工作量稍大,但是在保证幅度特性满足技术要求的同时,很容易做到严格的线性相位特性。

1 系统的总体结构设计

由于数字信号处理是用数值运算的方式实现对信号的处理,因此,相对于模拟信号处理,数字信号的处理具有灵活性、高精度和高稳定性、便于大规模集成、而且可以实现模拟系统无法实现的诸多功能。

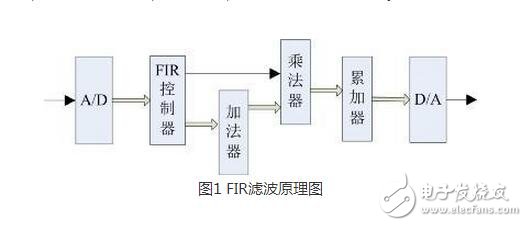

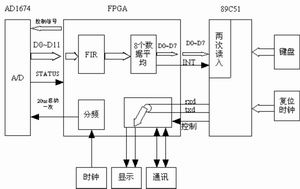

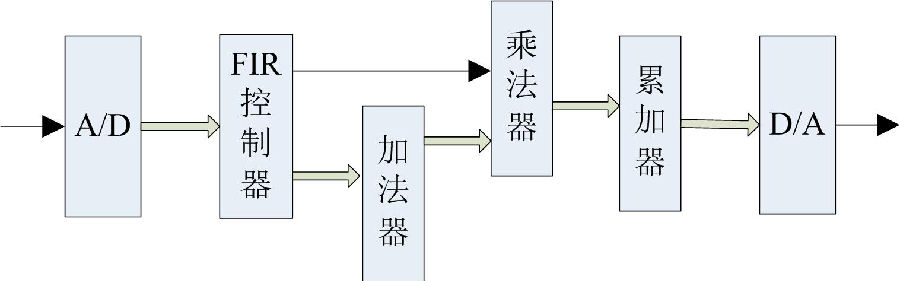

图1所示为数字滤波器的信号处理过程。数字信号处理的对象诸如语音信号等它们本身也是模拟信号,所以一般先经过缓冲以及模拟信号预滤波,然后利用模-数转换器(A/D转换器)将模拟信号转换成数字信号,再利用FPGA构成的FIR数字滤波器处理转换后的信号。进一步利用数-模转换器(D/A转换器)将数字滤波器处理过的结果转换为模拟信号供使用。

2 系统各部分功能的设计与实现

2.1 前端缓冲、预滤波以及模数转换部分结构

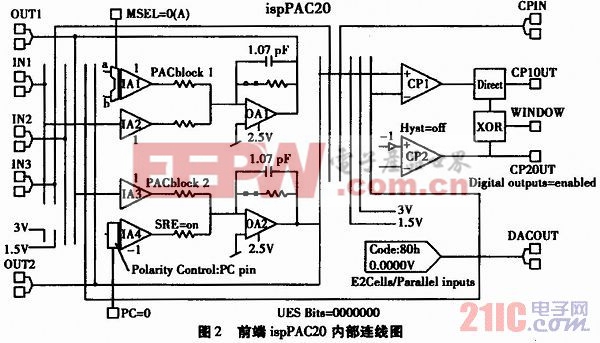

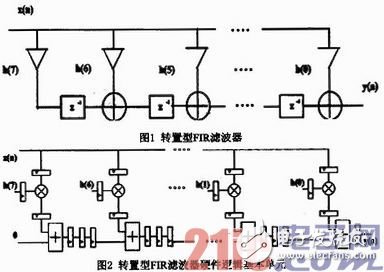

这部分的缓冲以及预滤波由ispPAC20来完成,然后利用FPGA以及ispPAC20中的D/A转换器、比较器共同构成逐次逼近式A/D转换器,其中ispPAC20中的电路结构图如图2所示。

评论