利用CPLD实现FPGA的快速加载

摘要:基于SRAM的FPGA由于其可编程、可升级的特性,被广泛应用于现代通信系统中。由于其易失性,每次上电后都需要重新对FPGA进行加载。随着通信系统复杂度的提高,FPGA配置文件越来越大,加载时间越来越长,严重影响系统的启动时同。为了提高FPGA的加载效率,在此提出一种通过CPLD进行FPGA串行加载的方案。通过验证,该方法既能能提高FPGA加载效率,又能节省CPU和FPGA的GIPO管脚,降低系统启动时间,非常适用于现代复杂通信系统。

关键词:CPLD;CPU;FPGA加载;PS加载

0 引言

现代通信技术发展日新月异,通信系统必须具备良好的可升级能力以适应时代的发展。现场可编程门阵列(Field Programmable Gate Array,FPGA)由于同时具备硬件电路高速运行和软件可编程的双重优点,被广泛应用于通信领域中。FPGA在上电后,需要加载配置文件对内部各功能模块进行初始化,而配置文件加载的效率直接影响系统的初始化时间。因此如何设计一种高效的FPGA加载方案,是通信系统设计中的一个重要环节。

文献的加载方案采用外部专用的E2PROM器件存储配置文件,并在上电后由FPGA控制整个加载过程。这种主动加载的配置方式需要专门的外部存储芯片,使用面窄,无法实现灵活的在线升级,并且由于EEPROM的容量有限,只能用于加载一些小的FPGA逻辑文件。文献提出采用CPU外挂FLASH存储配置文件,采用通用输入/输出(General Purpose Input/Output,CPU GPIO)管脾模拟被动串行(Passive Serial,PS)加载时序进行配置文件加载的方案,然而这种方案需要占用CPU宝贵的GPIO资源,虽然采用PS方式加载可以节省一定的管脚,但是由于CPU没有专门的PS加载控制器,必须通过软件控制GPIO来模拟PS加载的时序,对于软件最普遍使用的C语言,每一步操作都需要数条指令,耗费时间。对于有多个FPGA,要求远程升级,且对配置速度要求高的大型系统来说,这样的加载时间是无法忍受的。

本文介绍了一种基于CPLD加载FPGA的方案:FPGA配置文件被存放在CPU外挂的FLASH存储器中,加载时由CPU将配置文件读出,再通过连接CPLD的Local Bus总线将数据以并行方式送给CPLD,CPLD利用速度较高的时钟将数据串行送入FPGA。该方案既可以节省CPU和FPGA的管脚,又可以实现FPGA在线快速加载。

1 FPGA及其加载方式介绍

FPGA是一种可编程器件,用户可通过软件手段配置FPGA器件内部的连接结构和逻辑单元,完成所需的数字电路功能。目前市场上有三种基本的FPGA编程技术:SRAM,反熔丝和FLASH。其中基于SRAM的FPGA由于其速度快且具有可重编程能力,是目前应用最广泛的一种。但是这种FPGA是易失性的,每次掉电后,FPGA恢复白片,内部逻辑消失,上电时需要重新为FPGA加载配置数据。

大部分FPGA的加载方式都可以分为主动加载和被动加载。主动加载和被动加载最大的区别在于加载过程是由谁来控制,主动加载的加载过程是由FPGA自身控制,FPGA主动从外部存储器中读取逻辑信息来为自己进行配置,FPGA内部的振荡器产生加载时钟。

被动加载的整个加载过程都是由外部控制器控制,FPGA接收配置时钟,配置命令和配置数据,给出配置状态信号以及配置完成指示信号等。

为了选择一种合适的加载方式,这里将Altera公司FPGA产品的各种加载方式的对比于如图1所示。需要注意的是,配置速度的快慢只是相对的,其他一些因素如闪存的读取时间,驱动时钟频率等也会影响配置的时间。

从图中可以看到,并行加载方式虽然速度较快但是耗费较多的管脚;而串行加载则可以节省管脚、降低成本。在几种串行加载方式中,PS加载方式是大部分器件都支持的方式,因此本文后续的设计方案选择PS加载方式进行实现。

2 加载方案的设计

整个加载方案主要由硬件电路,CPLD逻辑,软件代码几部分组成。

2.1 硬件设计

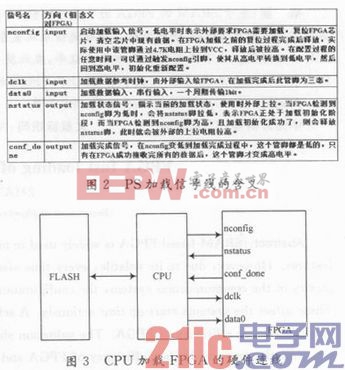

在第1节的讨论中选择了PS加载方式。PS加载一般要用到5根信号线,分别是nconfig,dclk,data,nstatus和conf_done,它们的含义如图2所示。

在传统的PS加载方式中,CPU与FPGA的连线如图3所示。

评论