AES加解密算法IP核的设计与实现

计算机科学技术中的数据加密是信息安全的重要手段。Rijndael加密算法由比利时密码学家JoanDaemen和VincentRijmen发明的一种迭代型分组加密算法,2000年被确定为美高级加密标准AES的最终算法。本文通过对AES算法的流程进行改进,提高IP核的性能,从而获得低成本高性能的AES加密实现方法。

本文引用地址:https://www.eepw.com.cn/article/189657.htm1 AES算法流程

AES算法是一个迭代型分组密码, 将输入的明文( 或密文)分成16个字节,在第一个轮密钥加变换后进入1O轮迭代。前9轮完全相同,依次经过字节代替、行移位、列混合、轮密钥加,最后一轮不同,跳过了列混合,解密与加密过程类似,但执行顺序与描述内容有所不同,因此AES算的加解密过程需要分别实现。

我们可以调整操作顺序,先进行密钥加操作,再进行列混合操作,密钥扩展部分的列混合操作就可去掉,从而密钥扩展模块被简化,AES IP核的硬件复杂度得到降低。

2 IP核设计方案

笔者将IP系统的工作模式设计为闲置模式、密钥输入模式、单轮加密模式及连续加密模式,其结构包括时序控制、密钥处理、数据处理三个主要单元。

2.1 密钥处理单元。

① 在系统进入密钥输入模式后,从数据输入端口连续四个时钟周期读入总共一百二十八位密钥数据,系统完成第一轮密钥的计算,回到闲置模式。② 密钥处理单元处于加密模式时,按算法需求实时计算各轮密钥,以三十二位为一单元输出,与数据通道中三十二位数据结合进行运算。③ 为利于下一轮加密的进行,密钥处理单元的复位环节是在系统模式由加密状态转为闲置状态时结束。

2.2 数据处理单元。

① 加密模式的主要工作是迭代运算明文数据。数据处理单元承担检测动能,当处于最后一轮数据运算时,会直接跳过列混合这一环节。② 加密模式下数据处理单元读取一百二十八位明文数据连续四次,再通过四十个时钟周期数据运算,密文之首个三十二位数据段得以产生。

2.3 时序控制单元。

该单元负责生成整个系统关键控制信号,因控制信号集中由一个单元负责产生,所以使得软件综合出较高的时钟频率,输出的时钟相位也趋于一致。从AES加密方法流程图中可以看到,第一轮与最后一轮都进行了特殊处理,虽然未经过完整的四轮处理过程,但在设计中将第一轮与最后一轮使用单独硬件实现,减少了两轮的运算时间。而且,降低资源占用的主要手段主要是减少Sbox的使用。

3 硬件实现方式

为使本硬件在上述设计的基础上得以实现,笔者采用的方式是: 应用QuartusII8.0软件形成Verilog HDL语言, 应用ModelSim6.2系统软件进行测试,路径与综合的分析工作应用FPGA综合工具Synplify9.pro辅助完成。

主要目的是:1)考察80 MHz频率下,目标器件EP1C4F324C6所综合的IP核的资源占用及性能。2)在EP2S15F484C3目标器件的高性能状态中再一次综合及后仿真,以便将测试结果纵向比较,得出测试结论。

3.1 测试过程。

密钥为:2b7e1516_28aed2a6_abf71588_09cf4f3c,输入明文:3243f6a8_885a308d_313198a2_e0370734输出密文3925841d_02dc09fb_dc118597_196a0b32,结果与预期吻合。

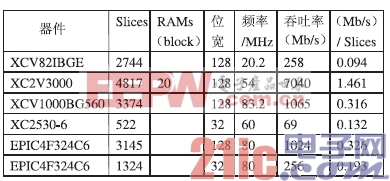

从建立流水作业以提高性能的目的出发,32位和128位数据位宽的设计中原文计算速度/资源比值时未考虑所占用的RAMs资源,而且文中设计为25MHz时钟频率,进行数据分析时却将工作频率直接换算为54MHz,而未对其设计是否可正常工作于此频率进行论证。得到数据见表1:

表1 硬件实现的比较

3.2 数据分析。

IP核在80MHz时钟频率下工作时,数据吞吐量为256Mb/s,速度/资源值为0.193。在位宽扩展时,采用并行连接IP核的办法,时序控制单元与密钥扩展单元可实现共用,进一步提高资源利用率。当扩展为128位数据位宽时,数据吞吐量成倍增加,而速度/资源比提高到0.326(见表1)。

3.3 实验结论。

本设计在32位数据位宽的同类设计中有一定的优势,采用6级流水线技术及复合域方法优化Sbox,达到了较优的设计指标。

在Synplify9下选定目标器件EP2S15F484C3,优先考虑提高速度,综合结果报告最高时钟频率超过240MHz,说明本IP核设计合理,较好地利用了目标器件资源。

本文设计的IP核硬件在输入、输出端加FIFO数据缓存器使从AES加密主器件被中断数据传输次数减少,而且在实际应用中、简化了方法流程图中可以看到,第一轮与最后一轮都进行了特殊处主器件操作时序,形成了标准通信界面,是一种低成本高性能理,虽然未经过完整的四轮处理过程,但在设计中将第一轮与的AES加密实现方法,整个设计具有较强的实用性,运行稳最后一轮使用单独硬件实现,减少了两轮的运算时间。而且, 定,效果良好。降低资源占用的主要手段主要是减少Sbox的使用。

评论