基于FPGA的面阵CCD成像系统设计

视频信号处理单元主要完成预放、滤波、相关双采样(CDS)、后置放大以及A/D转换等功能。本文采用集成图像处理芯片VSP2230。VSP22 30是一款集成图像处理芯片,它可以对CCD输出信号进行相关双采样,具有可编程暗电平校正、可编程增益放大器(放大范围为-6~42 dB)、将模拟信号转换为十位的数字信号等功能。

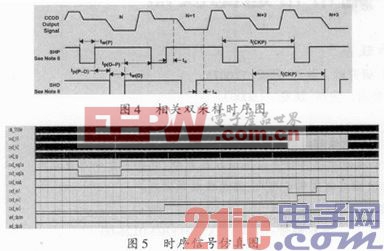

相关双采样(CDS)单元是对每个像元信号采样两次,分别获得参考电平和信号电平,将两个电平值的差作为CCD的输出信号,通过相关双采样可以滤除复位噪声、输出放大器的白噪声以及1/f噪声等。

具体模式见图4,在嵌位脉冲SHP的上升沿采集参考电平信号,在采用脉冲SHD的上升沿采集信号电平。SHP和SHD的位置很重要,对信号质量影响。很大,需要精细调整。ICX415AL芯片的每一行前端有3个哑像元,后端有38个暗像元,通过测量这些像元的电荷量,可以获得该款CCD的暗电平值,将上文的输出信号再减去暗电平值,就可去除暗电流噪声,输出更准确的信号。VSP2230芯片有两个引脚即用来完成该任务,即CLPDM和CPLOB引脚。

在CCD输出暗像元时,将CPLOB置为低电平,其他时候恒为高电平,在CCD输出哑像元时,将CLPDM置为低电平,其他时候置为高电平。本文引用地址:https://www.eepw.com.cn/article/189623.htm

最后将模拟信号经A/D转换为10位数字信号,输出给FPGA,再经图像采集卡输出至显示设备,即可观看到视频图像。

3 波形仿真结果

本设计采用Altera公司的Cyclone系列的EP1C12F25617芯片,在QuartusⅡ9.1集成开发环境下,运用VHDL语言进行编程,利用Modelsim SE 6.5仿真工具进行仿真,如图5所示,时序满足芯片手册要求。

4 实验结果

将用VHDL语言编写好的程序下载到FPGA中,用示波器检测波形无误后,接上CCD芯片,将图像信号经LVDS采集卡采集后显示于电脑上,如图6所示,由图可知,该CCD成像系统成像效果良好,符合设计要求。

5 结论

在分析了SONY ICX415AL行间转移型面阵CCD的驱动时序的基础之上,提出了基于FPGA的驱动时序发生器的设计方案,并使用VHDL语言实现了该设计方案。整个设计充分结合了FPGA器件的设计简单、调试灵活、性能优越等优点和VHDL语言的硬件描述能力强、便于学习和理解等优点。该CCD相机具有每秒50帧的帧频,适用于观测高速运动的物体,成像效果良好,目前已运用于实际工程中。

fpga相关文章:fpga是什么

电荷放大器相关文章:电荷放大器原理 热成像仪相关文章:热成像仪原理

评论