基于FPGA的AVS视频解码芯片仿真和验证平台设计

1.1.2 视频解码软件实现

在完成系统的硬件设计后, 利用Altera提供的Nios II IDE软件,实现应用程序的软件设计,主要是CPU控制主程序以及能够独立完成视频解码的软件程序。将待验证的硬件模块挂接到Avalon总线上,此时FPGA中既放入解码系统的硬件模块,也放入了解码系统的软件模块,RISC CPU 完成PC机上CPU的功能,控制系统软硬件模块的运行。待解码的AVS视频码流通过USB接口送给验证平台上的视频解码系统,RISC CPU协调放在FPGA中的AVS解码系统硬件模块和软件模块以完成解码。AVS数据经过解码,转换成可以播放的YUV格式的视频数据。

1.2 VGA显示设计

该部分将上述视频解码软件转换成的YUV数据经过视频控制器做一些后处理和视频格式转换的工作,然后将YUV视频数据通过VGA控制接口,最后在VGA显示器上将这些视频信号显示出来。下面分别介绍该部分的硬件开发设计和软件程序实现。

1.2.1 VGA显示硬件设计

在该设计中,Nios II软核处理器主要完成CFI-Flash和SDRAM存储器的读写操作,并且控制VGA的显示。在SoPC Builder中搭建VGA显示部分的硬件系统。针对系统的要求,在FPGA外围连接了SRAM、SDRAM和Flash等存储器,它们可以满足视频处理过程中对于存储器的不同要求。其中,SRAM作为CPU控制主程序运行的内存;Flash用于存储播放的YUV视频文件;SDRAM容量大、速度快,用于VGA显示的缓存,确保视频播放的流畅。并没有直接将SDRAM挂接到Avalon总线上,而是自己编写了SDRAM端口控制器,再将其挂接到Avalon总线上,通过端口控制器对SDRAM进行读写操作。

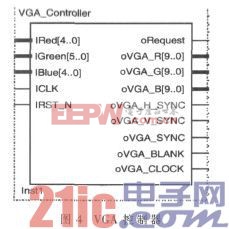

视频文件从Flash写到SDRAM后,再经过VGA控制器显示到显示器上。VGA控制器采用Verilog语言编写,使其具有更高执行性能,如图4所示。

1.2.2 VGA显示软件设计

在Nios II软件开发过程中,使用Altera提供的IO操作函数对SDRAM进行写操作,并且利用Altera提供的API函数对Flash进行读操作。具体函数如下:

Alt_flash_fd * fd

fd = alt_flash_open_dev(/dev/cfi_flash);

alt_read_flash(fd, CFI_FLASH_BASE+202752*j, buf, 202752);

for(i=0; i101376;i++)

{ IOWR_16DIRECT (SDRAM_0_BASE, 0, buf[i]);

2 验证实例

基于提出的AVS视频解码芯片验证框架,实现了基于FPGA的AVS解码芯片验证平台,验证平台分为视频解码系统和VGA显示系统两部分。视频解码系统可以嵌入待验证的硬件模块或下载待验证的视频解码器。基于该解码芯片验证平台,完成了AVS解码芯片以及其中帧内预测、熵解码和环路滤波等主要硬件模块的验证。相对于Modelsim的软件仿真,硬件验证平台大大提高了验证速度,同时也为成功投片提供了可靠保障。图5为验证平台中视频解码系统的软硬件解码过程。

在硬件系统设计过程中,FPGA验证已成为了系统设计的重要一环。本文提出了视频解码芯片的验证框架,并设计实现了基于FPGA的视频解码芯片验证平台。该硬件验证平台包括视频解码系统和VGA显示系统两部分,通过视频解码系统可以嵌入待验证的视频解码系统和硬件模块,提高了验证速度和效率。该验证平台具有操作灵活、验证效率高、可重用性强和易扩展为验证其他视频标准解码芯片的验证平台等优点。基于该验证平台已实现了多个硬件模块和AVS视频解码芯片的验证。

fpga相关文章:fpga是什么

pic相关文章:pic是什么

评论