FPGA在新型激光光幕靶中的应用

摘要:结合坐标采集和处理在新型激光光幕靶中的应用,针对传统激光光幕靶处理器I/O紧缺、处理速度慢、存在错报、漏报,无法测试子弹连发坐标等问题,提出了一种以FPGA为核心的坐标采集和处理系统的设计方法。设计中采用了自顶向下的设计方法,将该系统依据逻辑功能划分为3个模块,并在ISE 14.1和Modelsim中进行设计、编译、仿真,最后的仿真结果表明该系统能够很好地采集到子弹的坐标。

关键词:FPGA;激光光幕靶;坐标采集;Modelsim

弹丸的弹着点坐标测量是武器系统中不可缺少的一项重要指标,也是各种武器研制、试验和验收必须测试的重要参数。目前国内外测坐标方法很多,光电测坐标法以其测试精度高、可靠性好、成本低廉等优点常成为众多测坐标方案的首选,但传统的光电测坐标系统在坐标采集和处理方面也有不足之处。文献是目前国内应用的比较先进的测坐标系统,但是没有具体提到信号采集和处理的方法。文献实现了示靶、检靶、自动报靶的一体化,但在信号的处理方面有些不足。文献和文献是用单片机实现数据采集和处理,由于坐标精度的要求越来越高,要求光电传感器的间隔要足够小,因此需要较多的光电传感器。单个单片机I/O口少,需要多个单片机协同工作才可以组成完整的采集系统,系统结构复杂,而且子弹速度快,单片机频率低,实时性不是很好。文献是复杂可编程器件(CPLD)和单片机相结合的方式。文献是现场可编程逻辑器件(FPGA)和单片机相结合的方式。文献是用FPGA构成数据采集系统,但和文献一样,当靶面较大时,都需要几个其设计的采集处理单元拼接起来才能组成整个的采集处理系统。

针对这些问题,在新型激光光幕靶中采用了单片FPGA与并转串模块相结合,采集和处理相独立的方式,充分发挥了FPGAI/O口众多,响应速度快的特点。具有结构简单、安全可靠的优点,大大降低了成本,进一步增加了系统应用的灵活性。

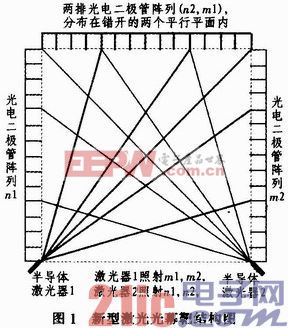

1 新型激光光幕靶原理简介

激光光幕靶是光电靶中的一种,它主要由激光系统和计算机系统组成。如图1所示,在前靶面(粗线光幕所在平面)的左下脚和与它平行的后靶面(细线光幕所在平面)的右下脚分别安装一个发光角度为90°扇形的大功率线状激光器。半导体激光器发出的激光束分别被玻璃柱透镜扩散成一个扇形光幕。由于前靶面和后靶面的距离为1 cm,所以可以认为这2个90度扇形激光光幕在同一个平面相互交叉组成一个大面积矩形光幕。子弹无论从哪个区域穿过激光光幕,都会遮挡住投射在某个或某几个光电二极管上的光线,当子弹穿过时至少有2排光电二极管阵列中的光电二极管会接收到信号。信号转换电路将光电二极管接收到的信号转换为数字信号,最后经采集处理后找到等效弹着点对应的光电二极管的标号,由此可以算出子弹穿过靶时的坐标。

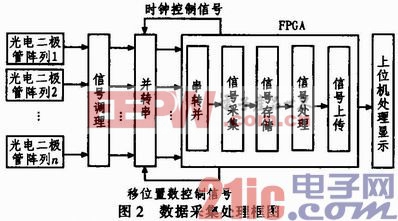

2 数据采集处理方法

根据靶面的大小以及光电二极管的间距,可以算出需要的光电二极管的数量,若以1mx1m靶,光电二极管间隔2.5 mm来算,四边大约需要4x400=1 600个光电二极管。不管是单片机还是CPLD、FPGA,都没有这么多I/O,需要几片拼接起来才能实现这么多I/O的采集。在本系统中采用并转串的方式,减少了需要的I/O数量.如80:1,则只需要大约20x3=60个I/O即可,则只要一块FPGA芯片就可以满足整个系统的要求。通过调整并转串的比例,在同一时钟的情况下,并转串的比例越小,FPGA对所有光电二极管阵列采集一次的周期就越短。如图2所示,光电二极管的光照状态经信号调理后变成FPGA可以识别的‘0’和‘1’信号。由FPGA控制并转串的时钟和移位、置数控制信号,采集到的信号经移位由高到低串行输入给FPGA,FPGA先由串转并模块保存为光电二极管阵列对应位数的信号,经处理,若判断为有子弹穿过,则将等效的坐标值上传给上位机处理显示。由于采用采集和处理相独立的方式,FPGA每隔5.34μs就采集一次数据,采集到有效数据就保存,FPGA按顺序处理并上传数据,避免了错报、漏报的情况,此外,由于处理速度比较快,完全可以满足子弹连发坐标采集的要求。

3 器件选型及依据

3.1 FPGA的选择及依据

FPGA是英文Field Programmable Gate Array的缩写,即现场可编程门阵列。本系统采用了Xilinx公司生产的Spartan 3E系列的XC3S500E型FPGA芯片。Spartan 3E是Xilinx公司性价比较高的FPGA芯片,本系统中XC3S500E采用了3.3 V电源供电,时钟频率为50 MHz,其系统门数为50万个,slice数目为4 656个,分布式RAM容量为73 kB,专用乘法器数为20个,DCM数目为4个,最大可用I/O数为232个,完全能满足系统的需要。

3.2 并转串芯片选择及依据

若子弹出膛时的初速约为1 000 m/s,弹头长约2.5cm。激光靶激光束宽2 mm,容易算出激光束被子弹遮挡的时间为:(25+2)/1 000 000=0.000 027 s=27μs,即光电二极管要采集的信号的频率为1/27 MHz=37 037 Hz。根据奈奎斯特(Nyquist)采样定理,采样频率应≥74 074 Hz,而在本系统中采样频率为187 265.92 Hz,约为37 037 Hz的5倍,满足要求。

74LS165是八位移位寄存器(并行输入,互补串行输出),Fm(最大时钟频率)为35 MHz。其工作原理:当移位/置数控制端(SH/LD)为低电平时,并行数据(A—H)被置入寄存器。当移位/置数控制端(SH/LD)为高电平时,并行置数功能被禁止,将锁存的八位置数信号从高到低移位串行输出。通过级联11块74LS165,就可以实现88:1的并转串比例,由于是由FPGA控制74LS165级联块的时钟和移位置数工作状态,最终又串行输入给FPGA,可以保证时序。若一个光电二极管阵列由88个光电二极管组成,则要级联11块74LS165,要把一个光电二极管阵列的所有光电二极管状态数据给FPGA需要89(88+1移位置数控制信号)个clkout,在本系统中1个clkout的周期是60 ns,则总时间t=89x60ns=5.34μs,约是子弹穿过时间的1/5。由于采用的是并行采集,各个光电二极管阵列是独立的,但又可看成是同一复制体,FPGA每隔5.34μs就可以采集到靶上所有光电二极管阵列的数据,实时性较好。

评论