FPGA工程师应如何挑选ADC和DAC

将具有信号处理功能的FPGA与现实世界相连接,需要使用模数转换器(ADC)或数模转换器(DAC)

本文引用地址:https://www.eepw.com.cn/article/189563.htm一旦执行特定任务,FPGA系统必须与现实世界相连接,而所有工程师都知道现实世界是以模拟信号而非数字信号运转的。这意味着需要在模拟信号域与数字信号域之间进行转换。针对手头工作选择恰当的FPGA时,用户面临着林林总总的选择,在为系统选择正确的ADC或DAC时也是如此,玲琅满目。

选择时首先要确定转换信号所需的采样频率。这个参数不仅将影响转换器的选择,同时也会影响对FPGA的选择,这样才能确保器件能够满足所需的处理速度及逻辑封装要求。转换器的采样频率至少为信号采样频率的2倍。因此,如果信号的采样频率为50MHz,则转换器采样频率至少应为100MHz。否则,已转换的信号将引起自身混叠,导致信号无法正确表示。但混叠并不总是一件坏事情;事实上,如果转换器的带宽足够高,那么用户可以利用混叠将信号混叠至可用的带宽。

我们可采用多种不同方法来构建模数转换器(ADC)。最常见的方法包括闪存、斜坡(Ramp)以及逐次逼近等。

1,闪存转换器以速度快著称,其使用一系列可扩展的模拟比较器对输入电压和参考电压进行比较;ADC利用这些比较器的输出来确定数字代码。

2,斜坡转换器可利用连接至DAC且可自由运行的计数器,对DAC输出/输入电压进行比较。当二者相等时,保持计数不变。

3,逐次逼近转换器(SAR)是斜坡转换器的另一种形式,其可利用DAC和比较器来处理模拟输入信号。但SAR转换器并非执行累计计数,而是通过判断计数的模拟表示是否高于或低于输入信号,并采用试错法(trial-and-error)来确定数字代码。

此外,数模转换器(DAC)也可以采用若干种方法来实现,最常见的方法包括二进制加权、R-2R梯形网络、脉宽调制。

4,二进制加权是速度最快的DAC架构之一。这些器件可将各逻辑比特的不同转换结果进行汇总。例如,电阻DAC将根据电流代码来导通或切断这些电阻。

5,R-2R梯形转换器采用阻值为R-2R的级联电阻结构。由于可以轻松生成并匹配高精度电阻,因而这类DAC的精度比二进制加权转换器更高。

6,脉宽调制(PWM)是最简单的DAC结构类型,可通过简单的低通模拟滤波器传递脉宽调制波形。这些器件通常应用于电机控制领域,但它们也可作为Σ-Δ转换器的基础。

众多专家级器件(specialist device)的制造商已成功开发其自有的内部转换架构,可根据用途尽可能提供适用于特定领域的最佳性能。每种器件在转换速度、精度以及分辨率方面都各具优劣势。在选择FPGA时,您需要考虑I/O数量、所支持的I/O标准、时钟管理、逻辑资源和存储器,以及其它与器件类型相关的具体参数:最高采样频率、信噪比(SNR)、无杂散动态范围(SFDR)以及有效位数(ENOB)等。

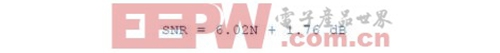

采样频率非常简单,是ADC能够数字化输入信号的最高速率。SNR表示信号与噪声电平的比值,与输入信号无关。用户可以利用以下公式来确定SNR的理论值:

其中N表示分辨率。该方程适用于满量程正弦波。

在系统测试过程中,用户可首先对输出执行快速傅里叶变换(FFT),然后测量输入信号与本底噪声的比值,这样即可确定实际的SNR值。

与此同时,SFDR表示输入信号与下一个最高峰值(通常为基谐波)的比值。通常SFDR用dBc来表示,会随着输入信号功率的降低而相应减小。

从转换器的测量结果可以看出,用户可利用下列式子来计算有效位数:

当进行这项测试时,应注意选择合适的FFT点数,从而确保不会由于一时疏忽而错误计算本底噪声。FFT点数不恰当将导致错误的计算结果。FFT本底噪声可通过下列式子计算得出:

用户应通过单音测试(通常为简单的正弦波)执行这些步骤,可降低输出频谱的复杂性。为了确保获取最佳结果,需要确保对输出信号执行相干采样。如果在数据窗口中包括几个周期,则执行相干采样。公式如下:

频谱

另一方面,用户在实现系统时还必须了解奈奎斯特准则,以确保正确地转换或量化信号。这意味着用户对所关注信号执行采样时,采样频率至少为该信号最高频率的2倍,才能确保正确进行转换。如果未按此标准执行采样,则将发生混叠;而如果没有正确理解混叠,则可能导致性能欠佳。

此外,因为这个原因,ADC需要利用抗混叠滤波器来阻止信号或噪声混叠至量化的信号中。但是,频谱混叠对于工程师来说非常有用,在ADC具有宽泛输入带宽的情况下尤为如此。经过周密安排考虑之后,混叠使用户无需借助下变频器即可直接转换信号。出于这种考虑,我们将频谱划分为几个区域。

利用表1中给出的信息,如果转换器拥有足够高的带宽,则可将信号从一个奈奎斯特频带混叠至另一个频带。

通信选择

正如所有的外部器件一样,ADC与DAC也配套提供了数个并行或串行接口选项。通常情况下,较高速器件用并行接口,较低速器件用串行接口。但是,可以根据您的应用选择采用特殊的接口方式。例如,采用串行接口比采用并行接口可以更轻松地检测出固定比特(stuck-atbit)。实际上,高速接口可提供多条输出总线(I和Q)或采用双数据速率(DDR)输出模式;有些器件甚至可能同时提供这两个选项。提供多条总线或采用DDR输出模式使用户能够保持数据速率,同时降低接口所需的运行频率。例如,如果接口的采样频率为600MHz,则其输出频率为300MHz(为采样频率的一半)。

如果时钟频率为75MHz(1/4采样频率)并且有两条可通过DDR对器件进行采样的数据总线,则可非常轻松地执行恢复操作。这类ADC对输入时序要求较为宽松。众多高速转换器均可利用其I/O中的LVDS信号,因为较低的电压摆幅和低电流可降低由其它信号标准所引发的耦合性,如LVCMOS等。这种耦合问题会影响转换器的混合信号性能。

模拟信号相关文章:什么是模拟信号

fpga相关文章:fpga是什么

模数转换器相关文章:模数转换器工作原理

脉宽调制相关文章:脉宽调制原理

评论