FPGA工程师应如何挑选ADC和DAC

DAC滤波

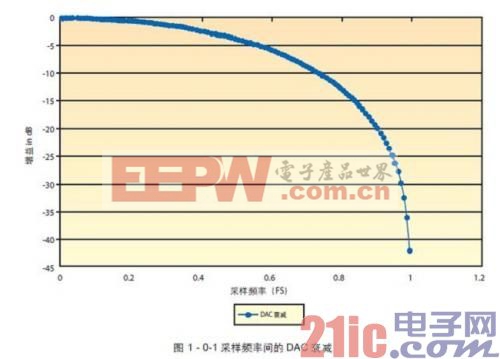

大多数DAC一直将模拟输出保持到下一个采样周期,这将对输出频率域产生良好的效果。用户将注意到这两个图像均存在于整个输出频谱中,由于在0.5FS时正弦效应将接近4dB(3.92dB),所有奈奎斯特区域中的输出信号都出现衰减(如图1所示)。这两大问题均可利用滤波器来解决。

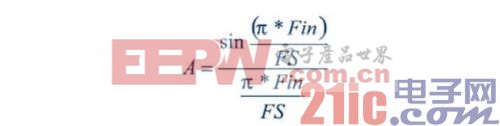

用户可以像实现FIR滤波器一样轻松实现正弦校正滤波器。开发该滤波器最简单的方法就是利用下列方程式来绘制正弦衰减特性。

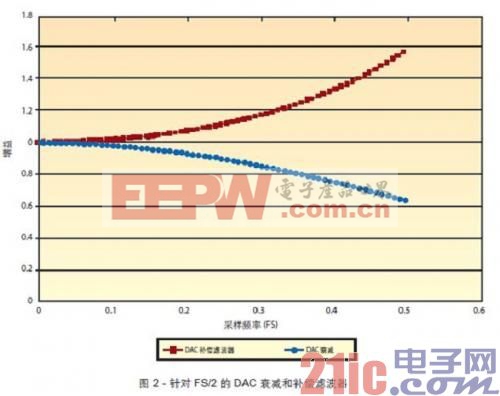

先创建校正因子,该因子是所计算出衰减系数的倒数,然后再执行逆傅里叶变换,以获取所需要设计滤波器的系数。通常情况下,用户需要采用几个抽头才能实现该滤波器。表2给出了滤波器的前11个系数,同时图2还给出了针对衰减的补偿。

在系统测试

众多这类系统都将利用转换器实现终端应用的具体性能特征,如CDMA或GSM等。为实现该项性能而进行的测试需要在测试系统(任意波形生成器、逻辑分析仪、模式生成器、频谱分析仪等)方面进行大量的投入。但是,FPGA高度的可重编程灵活性使用户能将特定的测试程序插入至器件中,这样既可以捕获并分析ADC的输出也可以提供DAC激励,从而减少对更多额外测试设备的需要。

转换101

由于FPGA通常需要与ADC和DAC接口相连,因而对于任何FPGA工程师来说,基本了解这些器件参数的重要性非常关键。如果用户计划在设计验证与调试过程中利用FPGA的可重编程灵活性来测试转换器的性能,这一点尤其有用。

模拟信号相关文章:什么是模拟信号

fpga相关文章:fpga是什么

模数转换器相关文章:模数转换器工作原理

脉宽调制相关文章:脉宽调制原理

评论