FPGA最小系统电路分析:下载配置与调试接口电路设

下载配置与调试接口电路设计

本文引用地址:https://www.eepw.com.cn/article/189541.htmFPGA是SRAM型结构,本身并不能固化程序。因此FPGA需要一片Flash结构的配置芯片来存储逻辑配置信息,用于进行上电配置。

以Altera公司的FPGA为例,配置芯片分为串行(EPCSx系列)和并行(EPCx系列)两种。其中EPCx系列为老款配置芯片,体积较大,价格高。而EPCSx系列芯片与之相比,体积小、价格低。

另外,除了使用Altera公司的配置芯片,也可以使用Flash+CPLD的方式去配置FPGA。

在把程序固化到配置芯片之前,一般先使用JTAG模式去调试程序,也就是把程序下载到FPGA芯片上运行。虽然这种方式在断电以后程序会丢失,但是充分利用了FPGA的无限擦写性。

所以一般FPGA有两个下载接口:JTAG调试接口和AS(或PS)模式下载接口。所不同的是前者下载至FPGA,后者是编程配置芯片(如EPCSx),然后再配置FPGA。

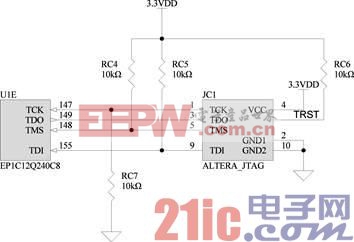

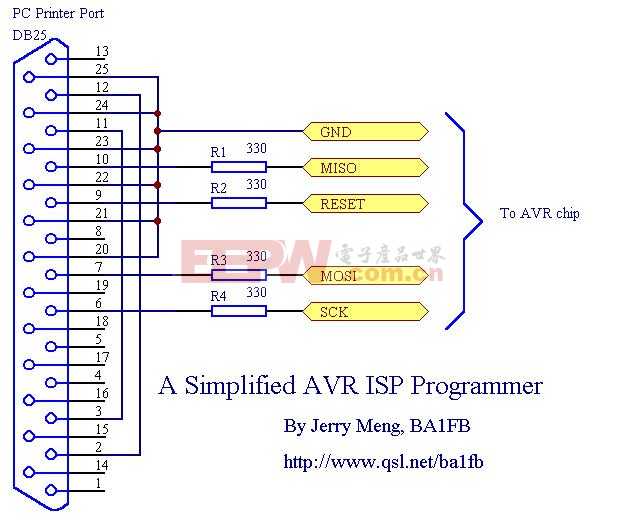

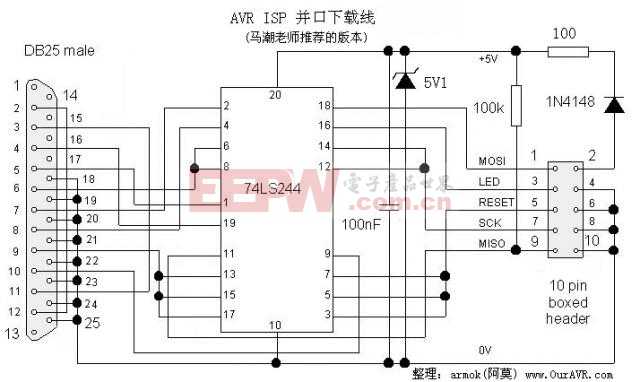

如图2.7和图2.8所示分别是JTAG模式和AS模式的电路原理图。

图2.7 JTAG模式原理图

评论