基于FPGA和USB2.0的高速数据采集系统

2.3 接口电路

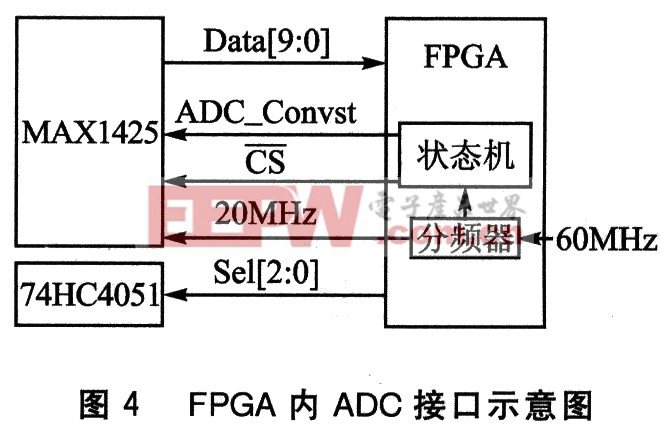

2.3.1 FPGA内的ADC接口模块

MAX1425和74HC4051的控制信号都由FPGA产生,接口电路如图4所示。本文引用地址:https://www.eepw.com.cn/article/188574.htm

FPGA的工作时钟为60 MHz,该时钟经过分频后,提供20 MHz给MAX1425作为工作时钟,同时也作为FP-GA内其他逻辑的工作时钟。由FPGA内状态机控制,当CS为低和ADC_Convst为高时,MAX1425进入采样保持状态。当Clock的第一个上升沿到来,MAX1425开始转换。RD输出为低时,MAX1425把转换结果放到数据总线上,FPGA开始读入10位数据(FD[15:0]中的10~15六位数据线悬空,使数据线和A/D的位数匹配)。FPGA控制寄存器的Sel[2:O]信号作为74Hc4051的通道选择信号,从8路模拟输入信号中选择1路作为MAX1425的输入。完成一次转换后,当ADC_Convst:再次为高时,开始下一轮转换。

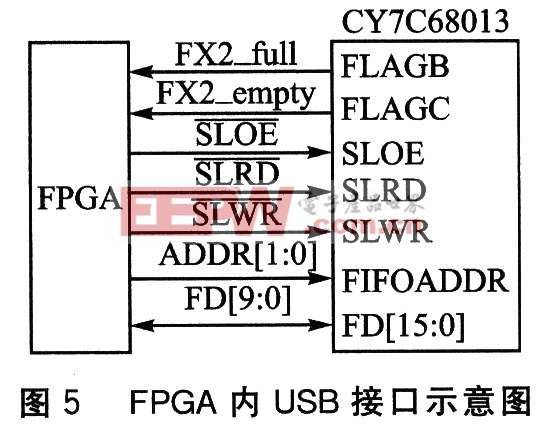

2.3.2 FPGA内的USB接口模块

图5是Slave模式下CY7C68013与FPGA的连接示意图。中间是FPGA中USB接口模块部分对应的信号。

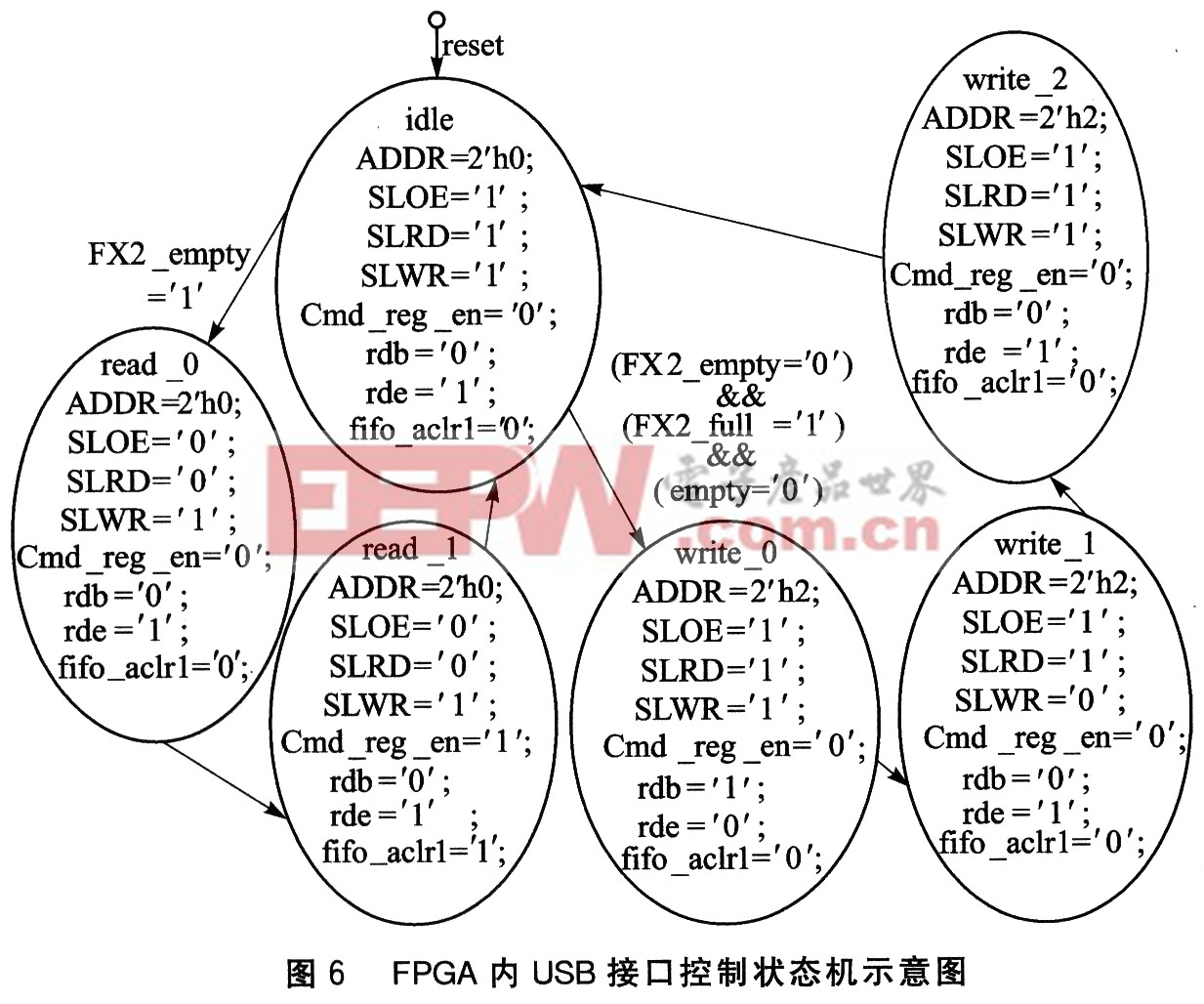

2.3.3 FPGA内的USB接口控制状态机

FPGA内USB接口控制状态机的状态转移图如图6所示。共有6个状态,复位信号的模式设置为异步复位。状态机主要分为读、写两部分:读取EP2中所包含的命令,存到FPGA的控制寄存器组中;将FPGA的FIFO中的数据读出,写入EP6端点缓冲区。

该状态机工作过程为:

①系统加电或复位后,状态机进入空闲状态(idle)。

②在空闲状态下,当EP2不为空时进入read_0状态,从EP2中读出PC机传来的控制命令。随后进入read_1状态,把命令存到FPGA内控制寄存器中,并把FPGA内的FIFO清空(fifo_ach1='1'),以准备存储采样数据。之后再回到idle状态。

③在空闲状态下,当EP2为空(FX2_empty='0'),而FPGA的FIFO不为空(empty='0'),且EP6不满时,进入write_0状态。之所以要看EP2是否为空,是想优先处理PC机通过EP2传来的命令。在write_0状态下,选中对CY7C68013的EP6操作(ADDR=2'h2),同时从FPGA内部的FIFO中读出一个数据。之后进入write_1状态,把数据写入CY7C68013。然后进入write_2状态,write_2状态的输出与idle状态相同,目的是提供一个时钟周期的延迟。因为FPGA工作于60 MHz的时钟下,比CY7C68013快,所以加入一个延迟以保证可靠的数据传输。

评论