3线总线收发器XE1201

XE1201是由XEMICS公司生产的RF收发IC,它将无线传输技术的发射与接收功能集成在单一芯片上,同时集成了高频发射、高频接收、PLL合成、FSK调制以及高速率、超低功耗等功能。XE1201可工作在433MHzISM频带和390~470MHz频带,其数据传输速率可达64kbit/s。另外,XE1201还采用了连续相位的2级频移键控(CPFSK)方式。

XE1201的接收部分除了具有滤波通道和接收所用的解调器外,还集成有低噪声放大器(LNA)和下变频器,它采用直接变频方式,其微控制器接口可直接对数据流进行处理,并可产生同步数据时钟(CLKD)。

XE1201的发射部分可完成从数据流到天线的传送,并提供了一个完整的通道,该部分带有一个可对频偏进行编程的直接上变频器,并可对其RF输出功率进行控制。

XE1201的最主要特点是其带有3线总线接口,并可通过该3线总线以及外部引脚来设置传输状态,仅需极少的外部元件(无线匹配网络、振荡电路、SAW振荡器)即可完成接收和发射双重功能。

XE1201的主要技术数据如下:

●电源电压:2.4V;

●RF敏感度:109dBm;

●数据传输速率:64kbit/s;

●发射功率:-5dBm;

●待机电流:<1μA;

●接收电流:6mA;

●发射电流:-5dBm时为8mA;-20dBm时为5mA。

●响应时间:<1s;

●频率偏离:125kHz。

2 工作原理

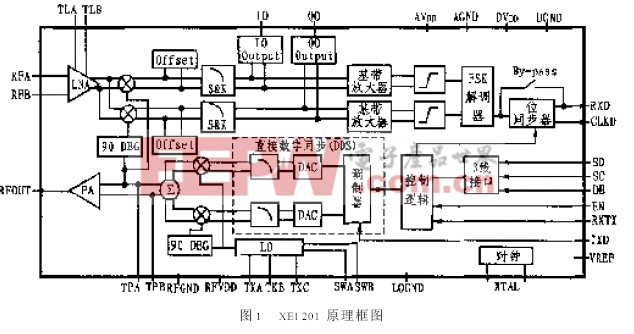

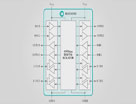

XE1201的原理框图如图1所示,各引脚功能描述如表1所列。由图1可以看出,XE1201主要由接收、发射、本振及3线总线接口四部分组成。

本文引用地址:https://www.eepw.com.cn/article/188573.htm

2.1 接收

XE1201型3线总线收发器中的接收部分由低噪声放大器(LNA)、下变频器、自激消除模块、基带滤波器以及位同步器等部分组成。其中LNA提供的低噪增益可通过外部电路(分立元件)进行调节,该外部电路由输出LC振荡电路和RF输入LC匹配网络组成;下变频器具有90°相移电路和2个合成器及其各通道(I/O),可用于完成零中频接收器的直接下变频;自激消除模块则用来对DC和低频输出信号进行50dB衰减,以避免本振上的自激振荡;基带滤波器由2个级联的Sallen&key低通滤波器组成,每级有10dB的增益,可实现具有30kHz关断频率的4级Butterworth低通滤波,其AC耦合(截止频率为64kHz)可以避免偏移量的增加,并可衰减1/f的噪声;而位同步器是一个可被ALU控制的数字PLL,它为系统提供同步数据时钟。为了提高其性能,可根据所需的数据速率来通过3线总线对位同步器进行编程设计。

2.2 发射

XE1201的发射部分由DDS调制器、单边带上变频器及功率放大器组成。它可直接通过数字合成器(DDS)来实现,由于XE1201的FSK频偏相当精确,并可通过3线总线进行调节,因此,I和Q基带可在抗干扰滤波器后直接上变频到UHF频段。

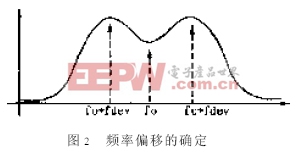

DDS调制器由数字和模拟两个模块构成。在数字模块中,其内部时钟设在2MHz,并由DDS将数据位流转换成正、余弦信号。当相位累加器为7位时,其频偏最小的步进频率(每位)为3.9kHz,频偏差(FSK)的可编程调节范围为0~127(7位)。因此,理论上它的范围为295kHz。开机时,频偏值为32(125kHz)。当Data为0时,f=fLo-fdev;Data为1时,则有f=flo+fdev。如图2所示。另外,也可对解调器的频率偏移进行调节以使其满足fdev=3906.25・n(Hz),其中n为无符号的7位字的十进制值,在数字模块中,fdev必须满足Filter BW>fdev>Data。而DDS模块中的模拟模块(DDSA)的任务是将正、余弦信号从DDS转换成模拟的I和Q信号,该转换通常由2个8位DAC来完成。

单边带上变频器可用于完成从基带FSK信号到UHF频率的频率转换。功放则可为天线发射RF信号提供驱动,但它并不能直接驱动天线,而需要有外部匹配网络。应当指出,该功放的输出功率也是可编程的(4级)。

2.3 本振

本振电路是以一个标准的SAW振荡器为基准,这个SAW振荡器可提供最快的开关时间,同时也可改变低功率UHF振荡器的频率。对于433MHz的ISM频带来说,SAW可在433.92MHz频率上产生谐振,其时钟产生信号可驱动一个90°的相移器,而这个相移应连到单边带上变频器。

2.4 3 线接口及内部寄存器

XE1201最主要的特点是可通过3线总线接口来对FSK频偏、时钟使能、RF输出功率和数据速率及其它辅助功能等进行设计编程。并可通过此接口和相关引脚来设置其接收、发射和待机状态。

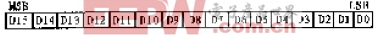

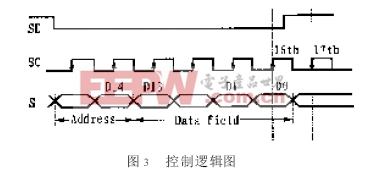

3线总线接口电路由3个内部寄存器(A、B、C)组成,它可在SC的上升沿采集数据位。其内部电路通过对SC的上升沿进行计数来检测输入数据的有效性,如果在SC上检测到的边沿数为16个,则数据将从输入移位寄存器转移到相应的寄存器中,图3所示为该寄存器的排列操作时序。其控制命令字的格式如下:

评论