基于FPGA和USB2.0的高速数据采集系统

实现数据采集与传输,可选择如下3种方法:

①使用传统的串/并口。传统的串口(如RS232),其传输速率为几十kb/s到100 kb/s,而系统所要求的数据传输速率很高,而且还要实现数据的采集与传输同步进行,串口的速率远远达不到实时要求;对于并口,虽然它的传输速率可达到1 Mb/s以上,但由于探测器与主机相距较远,因此走线比较复杂。

②采用通用的高速数据采集卡。高速数据采集卡(如ISA或PCI卡)虽然在数据存取速度上可满足系统要求,但仍然存在很多缺点,比如安装复杂,价格昂贵,兼容性不好,受计算机插槽数量、地址和中断资源的限制,可扩展性较差等。

③使用USB2.0通用串行接口总线。USB接口是一种重要的计算机外设接口,它支持热插拔和即插即用,使用非常方便。USB2.0支持高达480 Mbps的数据传输速率。USB接口可实现计算机与多个外围设备的简单、高速互联,将USB技术应用于数据采集是非常适合的。经综合考虑,本文选择采用USB2.0接口来完成对数据的采集与传输。

1 数据采集和传输系统方案设计

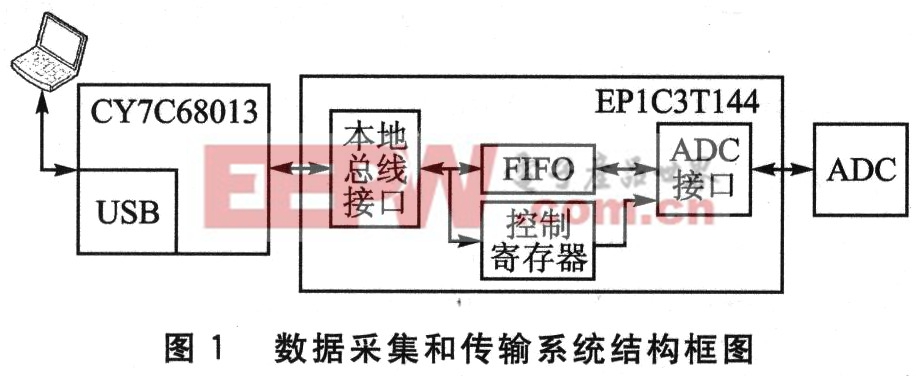

数据采集和传输系统主要由3部分组成,USB2.0通道、FPGA和A/D转换器组成,如图1所示。

CY7C68013是Cypress公司推出的EZ-USB FX2系列智能USB接口芯片。其作用是将主机所发送的命令序列经USB2.0端口输出,实现对数据采集系统的控制;同时把A/D转换器采集的数据以高速的数据序列形式发送到主机。其中,USB2.0端口提供一个能和计算机连接的数据传输接口。

FPGA利用内部的SRAM提供数据输入/输出的双缓冲功能。采用双缓冲的原因同USB中的大端点所配置的双缓冲类似,均是防止数据的溢出和保证数据传输的连续性。本文选用Altera公司的CycIone系列芯片EP1C3T144。

A/D转换器将所要采集的模拟量转换成数字量,通过滤波和放大后,由FPGA接收、缓冲、存储,经USB2.0端口传回至主机工作站。高速A/D转换器采用转换速率为20 MHz的MAX1425。

系统工作过程为:主机通过CY7C68013给数据采集系统一个采样控制命令,存入FPGA的控制寄存器中。FPGA根据该命令向A/D转换器发出相应控制信号。由于ADC采样频率为10 MHz,为和PC运行速度相匹配,在FPGA内部生成一个FIFO缓存器。A/D转换器在FPGA的ADC接口控制电路控制下,把模拟信号转换成数字信号,并将指定通道的采样数据存入FPGA内部FIFO缓存。同时,FPGA的USB接口控制逻辑查询CY7C68013是否空闲,如果空闲,那么由FPGA的USB接口控制逻辑将指定通道的采样结果,从FPGA内部FIFO缓存送入CY7C68013的内部FIFO。当内部的FIFO容量达到一定程度后,CY7C68013自动将数据打包传送到PC机。由于固件程序把CY7C68013设置为特定的自动模式,因此CY7C68013把数据送往PC机期间的所有操作无需CY7C68013中CPU的干预,从而保证足够的数据传输速率。采样过程中FPGA的USB接口控制逻辑依次取走批量数据,在USB接口打包传送时A/D转换持续进行,FPGA内部FIFO也被持续写入转换结果。

评论