MOSFET栅漏电流噪声模型研究

CMOS器件的等比例缩小发展趋势,导致了栅等效氧化层厚度、栅长度和栅面积都急剧减小。对于常规体MOSFET,当氧化层厚度2 nm时,大量载流子以不同机制通过栅介质形成显著的栅极漏电流。栅极漏电流不仅能产生于沟道区域,而且能在栅极与源/漏的交叠区域产生。穿越栅氧化层的电流增加了电路的泄漏电流,从而增加了电路的静态功耗,同时也影响MOS器件的导通特性,甚至导致器件特性不正常。栅漏电流增加成为器件尺寸缩减的主要限制因素之一。

栅氧化层越薄,栅漏电流越大,工艺偏差也越大。栅漏电流噪声一方面影响器件性能,另一方面可用于栅介质质量表征,因此由栅介质击穿和隧穿引起的栅电流涨落为人们广泛关注。为了更好地描述和解释栅电流涨落对MOS器件性能的影响,迫切需要建立栅漏电流噪声精确模型。MOS器件噪声的研究,始于60年代,至今已有大量研究报道文献。而栅漏电流大的MOS器件噪声特性的研究仍是现今研究中活跃的课题。尤其当MOS-FET缩减至直接隧穿尺度(3 nm)时,栅漏电流噪声模型显得尤为重要,并可为MOSFET可靠性表征和器件设计提供依据。文中基于MOSFET栅氧击穿效应和隧穿效应,总结了栅漏电流噪声特性,归纳了4种栅漏电流噪声模型,并对各种模型的特性和局限性进行了分析。

1 栅漏电流噪声模型

(1)超薄栅氧隧穿漏电流低频噪声模型。

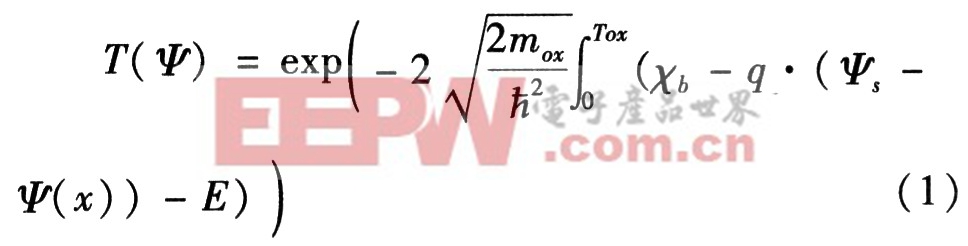

模型基于泊松方程与薛定谔方程自洽数值求解,采用一维近似描述了器件的静态特性,模型考虑了栅材料多晶硅耗尽效应和量子力学效应。在描述超薄氧化层的栅漏时,同时考虑了势垒透射和界面反射,电子透射系数表达式为

其中,χb为势垒高度,ψ(y)为位置y处的电势,E为隧穿电子能级。

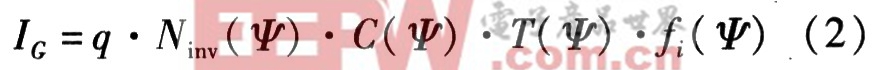

总栅隧穿电流为

其中,Ninv(ψ)为反型层电荷,C(ψ)为取决于界面反射的修正系数,fi(ψ)为频率因子。

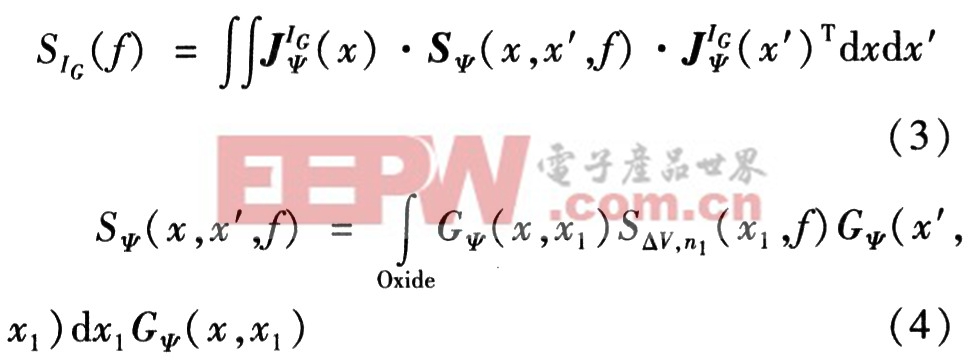

氧化层内部的缺陷对栅漏电流涨落的贡献,已在格林表达式中考虑和体现。这种近似允许摈弃等效平带电压涨落的假设,由此得到的栅电流涨落谱密度为

其中,![]() 为与静电势ψ(y)相关的栅电流,IG的雅可比矩阵,Gψ(x,x1)为氧化层x1处的单位电荷在氧化层x处的电势ψ(x)的格林函数。

为与静电势ψ(y)相关的栅电流,IG的雅可比矩阵,Gψ(x,x1)为氧化层x1处的单位电荷在氧化层x处的电势ψ(x)的格林函数。

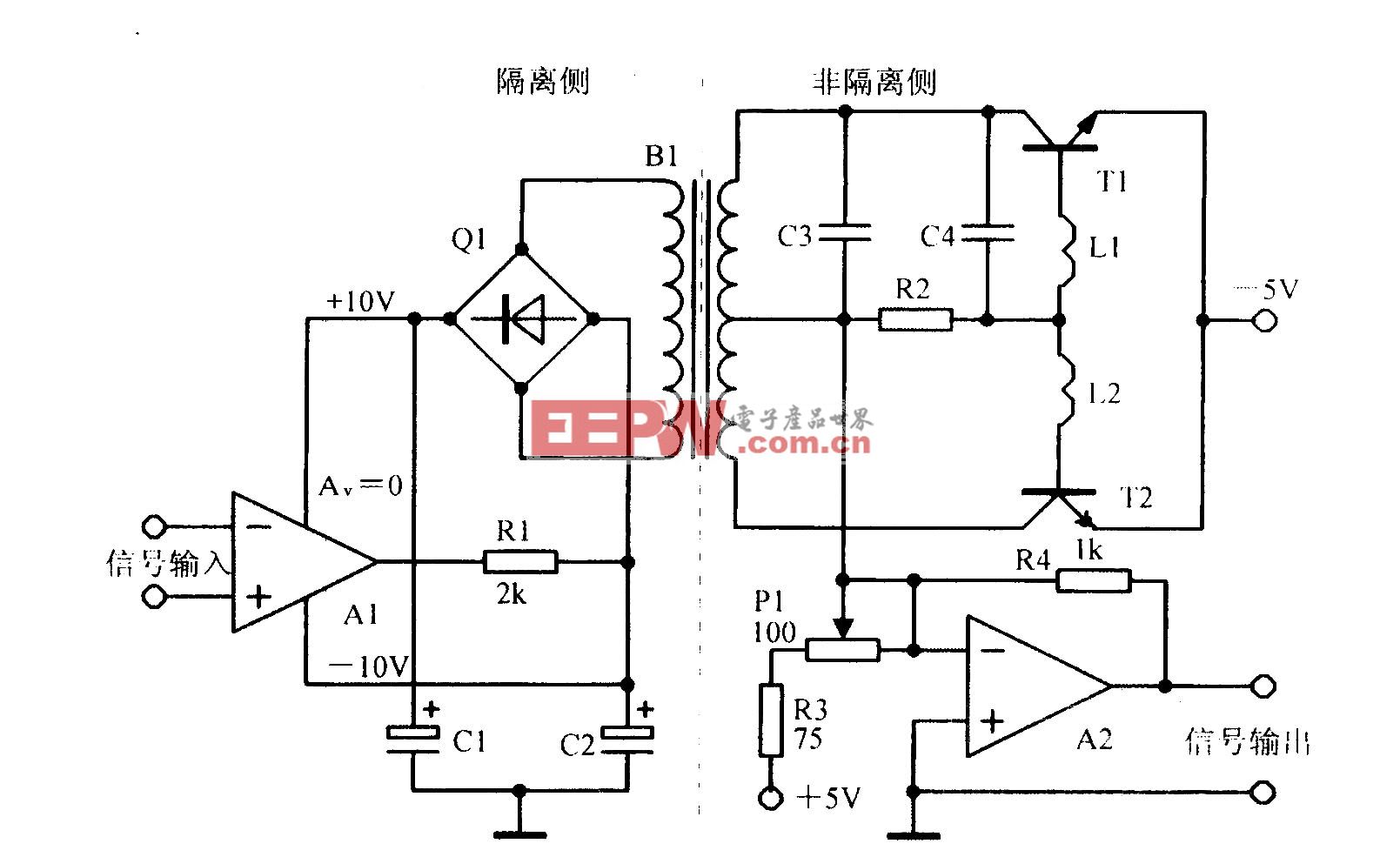

基尔霍夫电流相关文章:基尔霍夫电流定律

评论