一种单端10-bit SAR ADC IP核的设计

摘要:本设计通过采用分割电容阵列对DAC进行优化,在减小了D/A转换开关消耗的能量、提高速度的基础上,实现了一款采样速度为1MS /s的10-bit单端逐次逼近型模数转换器。使用cadence spectre工具进行仿真,仿真结果表明,设计的D/A转换器和比较器等电路满足10-bit A/D转换的要求,逐次逼近A/D转换器可以正常工作。

关键词:D/A转换器;逐次逼近;低功耗;单端;二进制加权电容

随着集成电路和数字信号处理技术的快速发展,我们可以在数字域里实现比模拟域里更高精度,更快速度,更低价格的各种信号处理功能,因此,模数转换器作为模拟系统和数字系统的接口就变得非常重要。而在各种类型的模数转换器当中,逐次逼近型的模数转换器(SAR ADC)因为其低功耗,中等精度和中高分辨率而得到了广泛的应用。而SARADC从输入来分,可以分为单端输入和双端(全差分)输入。虽然一个双端SAR ADC电路架构可以获得更好的共模抑制比和和较少的失真,而得到了广泛的应用,但在现实生活中对单端的ADC仍有一定的需求,如光栅尺中绝对码道信号的检测。本文则是在一种常见单端SAR ADC电路架构的基础上,对D/A转换器进行了改进,在不增加电容面积的情况下,减小了D/A转换时电容和开关所消耗的能量,减小了电容阵列转换的建立时间。

1 ADC整体电路设计

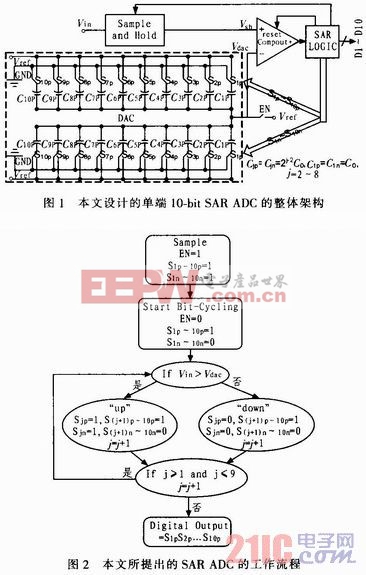

本文设计的单端SAR ADC的整体架构如图1所示,主要包括以下4个部分:采样保持电路(Sample and Hold)、比较器(Comp)、10-bit逐次逼近寄存器及控制电路(SARLOGIC)、D/A转换电路(DAC)。

输入电压Vin通过采样保持电路得到采样电压Vsh,Vsh与DAC的输出Vdac通过比较器进行比较,比较结果传递给逐次逼近寄存器,逐次逼近寄存器一方面输出比较结果,另一方面控制DAC的转换开关,以便进行下一位的转换。

1.1 SAR ADC的工作流程

SAR ADC的工作流程如图2所示,它主要可以分为采样、清零阶段和比较阶段。

第一步:采样、清零阶段。采样保持电路中的开关S,闭合,Vin=Vsh,属于跟随阶段;DAC中的电容C1p~C10p和C1n~C10n的下级板全部接GND,开关EN闭合,Vdac接GND,DAC处于清零阶段。

第二步:比较阶段。采样保持电路中的开关Sa断开,Vsh为采样得到的电压;DAC中的电容C1p~C10p的下级板接Vref,其余开关不动,而开关EN断开,此时DAC的输出结果:

Vsh与Vdac进行比较,如果Vsh大于Vdac,则比较器输出为1,即D1=1,而逐次逼近寄存器根据比较结果,将电容C10n(MSB电容)的下级板偏转到Vref;反之D1=0,C10p的下级板偏转到GND。其余电容保持不变。

第j步:根据上一步比较的结果,得到DAC的输出如下:

Vsh与Vdac进行比较,如果Vsh大于Vdac,则比较器输出为1,即Dj-1=1,而逐次逼近寄存器根据比较结果,将电容C(11-j)n的下级板偏转到Vref;反之Dj-1=0,C(11-j)p的下级板偏转到GND。其余电容保持不变。直至j=11,比较结束,进入下一个转换周期。

评论