Cortex-M4内核微处理器DMA方式的高速A/D采样

1 MK60N512VMD100微处理器简介

MK60N512VMD100芯片是基于Cortex-M4内核的典型芯片,是飞思卡尔Kinetis系列中集成度最高的芯片。Cortex-M4内核是在Cortex-M3内核的基础上发展起来的,其性能比Cortex-M3提高了20%。Cortex-M4在Cortex-M3的基础上强化了运算能力,增加了浮点运算控制器、DSP和并行计算等。MK60N512VMD100具有丰富的通信接口,主频高达100MHz,32路DMA供外设和存储器使用,大大提高了CPU利用率,具有33路单路和4路差分的16位A/D转换器、2路12位D/A转换器等外设。

2 MK60N512VMD100芯片DMA和ADC介绍

Kinetis系列微处理器都含有DMA,在最小的CPU干预下最高可提供32路DMA供外设和存储器使用,大大提高了CPU的利用率。DMA通道复用器(类似多路选择开关)可以把最多63个DMA请求源和16个DMA通道中的任意一个映射到一起。16路独立可选的DMA通道中,前4路还具有自触发功能。DMA复用器有3种工作模式:禁用模式、普通模式和周期触发模式。本文就介绍用周期触发模式实现高速A/D采样功能。

DMA通道复用器除了提供正常的映射功能外,前4个通道还提供了周期触发功能,由周期性中断定时器(PIT)触发,这种机制能够实现在没有CPU的干预下传输字节、帧或数据包。这种触发功能可用于任何支持DMA传输的外设,最常用的应用包括以下两种情况:

①定期轮询一个特定的总线上的外部设备。例如:一个SPI总线作为源被映射到DMA通道0,一旦设置成功,只要SPI的发送缓冲区是空的就会请求DMA传输,从内存中复制数据到缓存。SPI传输通过此通道上的一个触发器每3μs(举例)自动执行一次。在SPI接收端,SPI和DMA可配置成把接收到的数据传到内存,在无需处理器干预的情况下有效地定期从外部没备读取数据送到内存中。

②利用GPIO端口产生或者采样波形。通过配置DMA将数据传送到一个或多个GPIO端口,可以使用存储在存储器中的表格数据产生复杂的波形。相反,使用DMA从一个或多个GPIO端口读取数据,是可以采样到复杂波形的,并把数据存储到内存中。

MK60N512VMD100芯片的ADC模块具有线性逐次逼近算法与高达16位的分辨率,4路差分1 6位A/D转换和24路单端外部模拟输入。输出模式有差分16位、13位、11位和9位几种模式,单路支持16位、12位、10位和8位模式,并且输出无符号数右对齐格式。

当应用程序需要连续采样时(每秒6 000个采样点),CPU可能会有相当大的负担。虽然使用可编程延迟模块(PDB)可能会减少一些CPU的负载,但是ADC支持DMA请求功能在高速采样时能获得更高的性能,ADC在转换完成后通过DMA中断请求触发DMA。本文就介绍此种方法。

3 软件设计

3.1 DMA周期触发方式相关寄存器的设置

(1)DMA通道配置寄存器(DMAMUX_CHCFGn)

DMA通道配置寄存器(DMAMUX_CHCFGn)数据格式如图1所示。

bit7(ENBL):DMA通道使能,设置为0则通道禁用,为1则通道使能。

bit6(TRIG):DMA通道触发使能,设置为0则触发禁用,为1则触发使能。

bit(5:0)(SOURCE):DMA通道源。

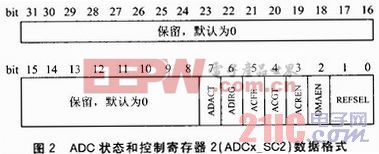

(2)ADC状态和控制寄存器2(ADCx_SC2)

ADC状态和控制寄存器2(ADCx_SC2)数据格式如图2所示。

bit7(ADACT):转换状态位,当一个A/D转换开始时ADACT被置位,当一个转换完成或中止时ADACT被清零。

bit2(DMAEN):设置为0则DMA功能禁用,为1时DMA使能。当一个ADC完成时发出 ADCDMA请求。

评论