一种数字射频存储器的设计

引 言

现代电子战孕育了DRFM的诞生,数字射频存储器是一种对射频信号采样、存储、运算然后转发的电子部件。DRFM对样本信息保存下来后,根据需要加入调制信息;再通过高速DAC转发出去,实现对目标的有效干扰。随着大规模集成电路、微波集成电路的高速发展,数据采集和波形产生的工作带宽已越来越宽,信号处理的速度也越来越快,这些都使得DRFM的成本大幅降低,而处理能力大大提高,从而得到了更为广泛的应用。

1 基本原理

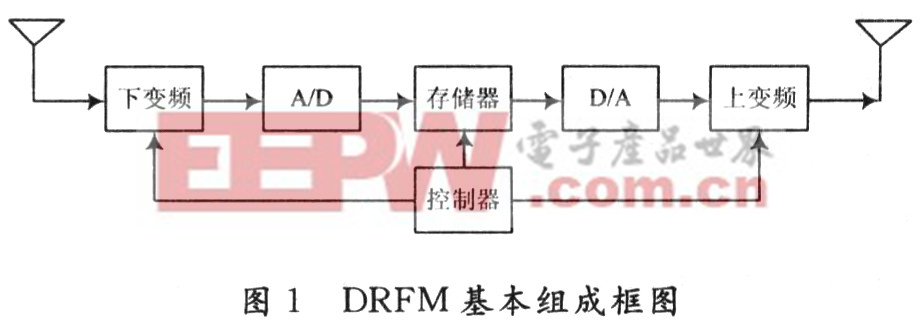

接收系统将天线下来的射频信号经过放大、滤波、下变频为中频信号,高速数据采集在基带或中频完成模拟信号的数字量化,数据采集的采样率决定着DRFM的接收带宽。数字样本信号被存储在存储器中,在需要时可随时读取出来并加适当的处理,然后由高速数/模转换器转换为模拟信号,再经激励上变频变频到所需频段,释放有效干扰,其基本组成框图如图1所示。

2 硬件设计

考虑到所需设计的DRFM带宽宽,存储容量大,信号处理运算量大,整个DRFM分为高速数据采集、信号处理单元、干扰波形(高速D/A)3部分,且来分开设计。数据采集和信号处理单元的数据传输采用光纤传输方式,信号处理单元和干扰波形之间的通信采用TS101的LINK口传输方式。

2.1 高速数据采集的设计

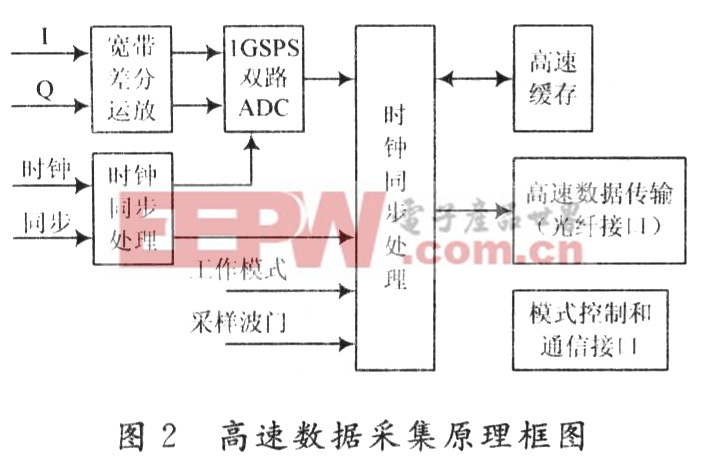

高速数据采集完成对正交的基带I,Q基带信号进行模/数转换、存储,再以光纤传输方式将样本信息送给后续信号处理单元。模/数转换芯片是数据采集的核心器件,这里采用Atmel公司的ADC芯片AT84AD001,其为采样率1 GHz、分辨率为8 b的双路ADC,输入电平峰峰值500 mV,16路LVDS电平输出和FPGA接口。FPGA采用Altera公司的EP2S90F1020。它集成了数百对差分管脚和大量的普通I,Q脚,方便与ADC和片外SRAM接口。其片内丰富的PLL资源使得时钟的产生变得更加容易。片外大容量的片外存储器(GS864436)保证了样本的海量存储。GS864436是总线速度高达200 MHz的SRAM,每片容量为2 M×32 b。由于ADC的采样率为1 GHz,就单路I来降数据率为1 GHz×8 b,如此高的数据率显然难以直接和SRAM接口。数据将在FPGA被降速为125 MHz ×64 b后再送到SRAM中。因此实际应用中2片存储器拼接为64 b后用来存储I路数据,2片存储Q路数据。和信号处理单元接口的光纤采用Agilent公司的2.5Gb/s光模块。该光模块为双向光纤,一个通道发送数据,一个通道接收。其原理框图如图2所示。

评论