一种数字射频存储器的设计

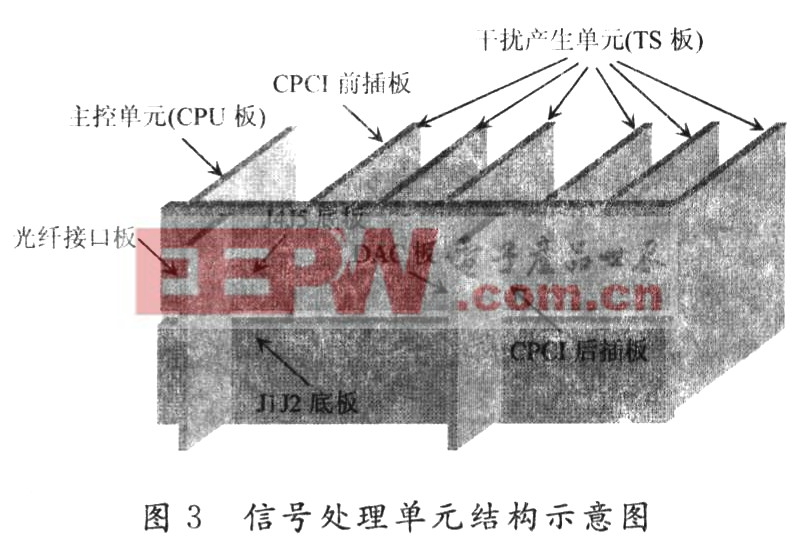

(3)存储容量。每个TS101片内带有6 MbSRAM,4片TSl01共享SDRAM最高2 GB,另外有2~4 MB ZBTSRAM内存。信号处理单元系统结构如图3所示。本文引用地址:http://www.eepw.com.cn/article/157923.htm

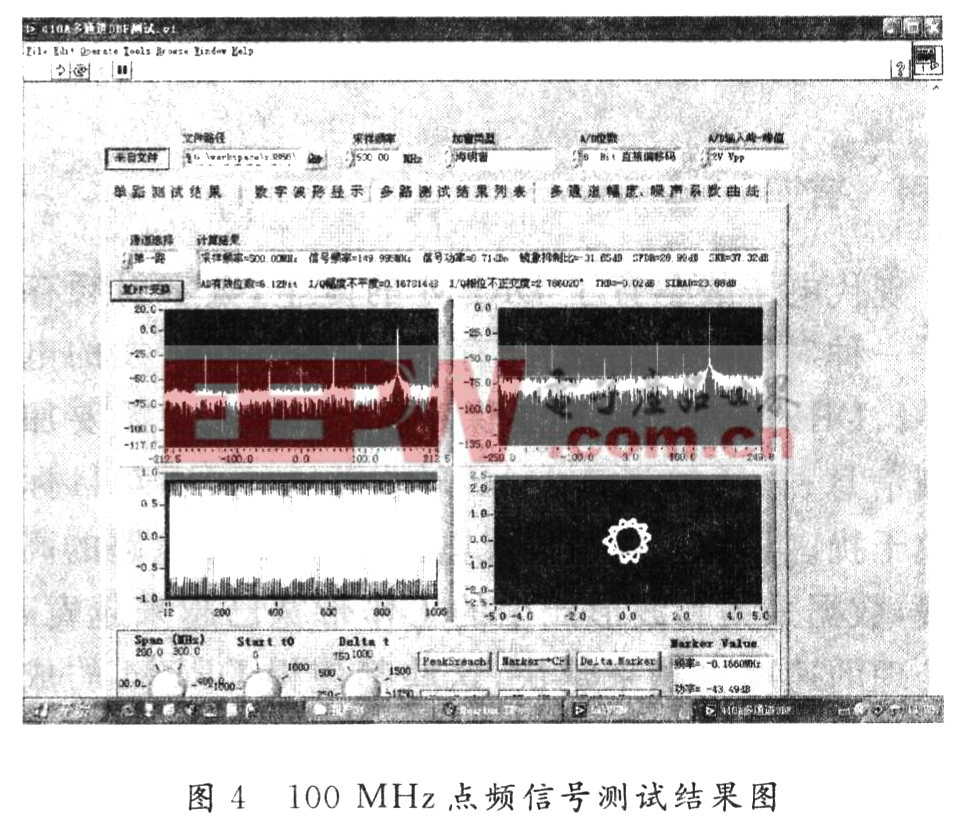

图4为频偏100MHz信号经过接收机变频、基带解调为I,Q信号,再经过数据采集量化、存储、光纤传输后。在光纤接口板上所测的各项性能指标。图中可以看到:A/D的SNR为37.2 dB,镜像抑制度为33.55 dB,A/D有效位数达6.12 b。上述指标证明了接收机及高速数据采集设计的正确性。

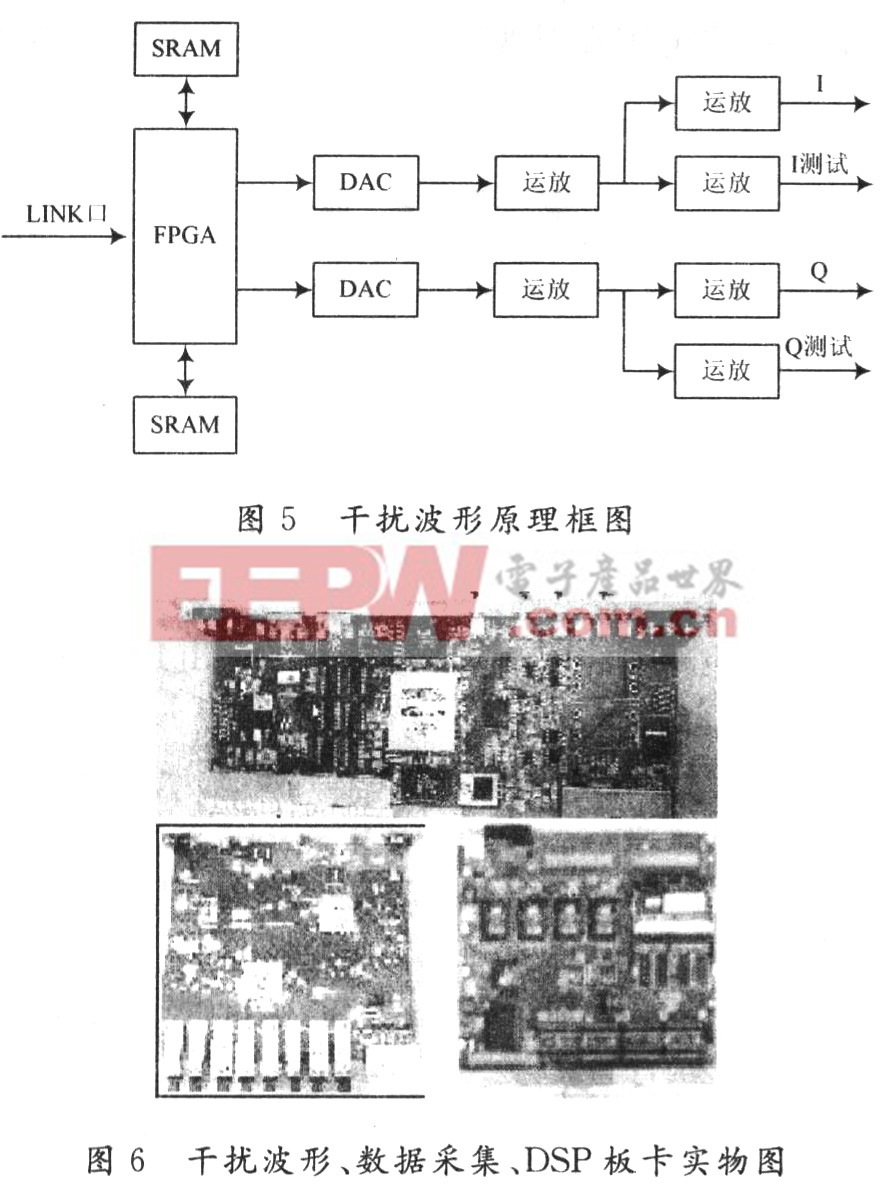

2.3 干扰波形(高速DAC)设计

干扰波形通过LINK口接收信号处理DSP板卡发送过来的基带I,Q数据.并用片外SRAM对数

评论