一种基于DDS+PLL的Chirp-UWB信号产生方案

同传统的脉冲超宽带(IR-UWB)相比,线性调频超宽度(Chirp-UwB)以其发射效率高,频带选择灵活,抗多径能力强,容易实现模拟匹配检测等突出优点,已逐渐成为超宽带技术领域的研究热点。

然而,对于宽带Chirp-UWB信号的产生一直是个难题。利用直接数字合成(DDS)产生可以获得高线性度、高稳定性的信号波形,但是由于模数转换器(DAC)速度的限制以及输出幅度受SINC衰落的影响,其输出信号带宽一般最高为100~200 MHz。利用模拟锁相环(PLL)虽可以产生很宽的带宽,可是受PLL自身惰性环节的影响,调频时间慢,转换速率低,且因其受锁相精度及压控振荡器(VCO)电调线性度的影响,还需要进行非线性补偿,这使电路趋于复杂。本文提出一种基于DDS+PLL的Chirp-UWB信号产生方案。该方案把频率稳定度好,输出频率分辨率高,频率转换速度快,相位噪声低的DDS与模拟PLL结合,取长补短,可以获得高频率分辨率、快的信号建立时间、低相位噪声和宽输出频率范围的高质量Chirp-UWB信号。

1 系统结构

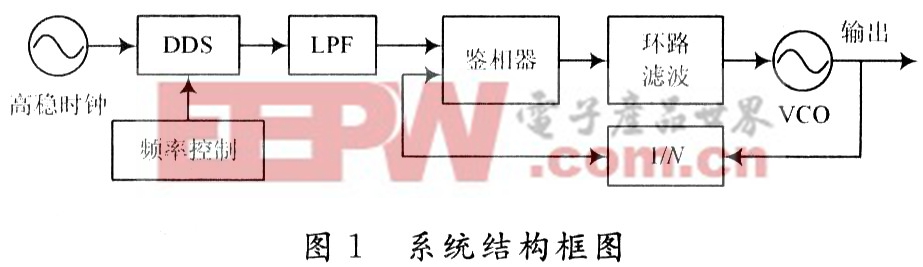

DDS结合PLL产生Chirp-UWB信号的系统结构如图1所示。

本方案由DDS产生的窄带Chirp信号作为PLL的参考信号。VCO产生的高频振荡经N分频后,在鉴相器(PD)中与DDS产生的窄带线性调频信号进行相位比较。系统稳定后,VCO产生的高频振荡经N分频后,其信号与DDS产生的窄带chirp信号的扫频线性度和频率稳定度一致。在这个方案中,PLL实际起到了倍频的作用,即将DDS输出的高线性调频信号进行了N倍的倍频。由于DDS输出频率和带宽可以编程控制,这种方式产生的Chirp-UWB带宽是可控的,在设计上具有很大的灵活性。

2 系统设计与仿真

本系统主要由参考信号发生电路,锁相环电路两部分组成。对于锁相环电路,射频仿真软件ADS提供有专门的元件库(System-PLL components),可以利用其中的元件快速建立锁相环的电路模型。然而,基于DDS产生的参考信号则由锯齿波控制线性VCO来实现,只要合理设置参数,这种等效并不会影响系统性能。下面对电路的各部分的设计进行分析。

2.1 参考信号产生

参考信号的产生可通过数字正交上变频芯片AD9857实现,中心频率设为100 MHz,Chirp信号的带宽设为7 MHz。利用ADS仿真时由锯齿波控制线性VCO,即可产生一个窄带Chirp信号作为锁相环的输入参考信号。

2.2 鉴相器和分频器

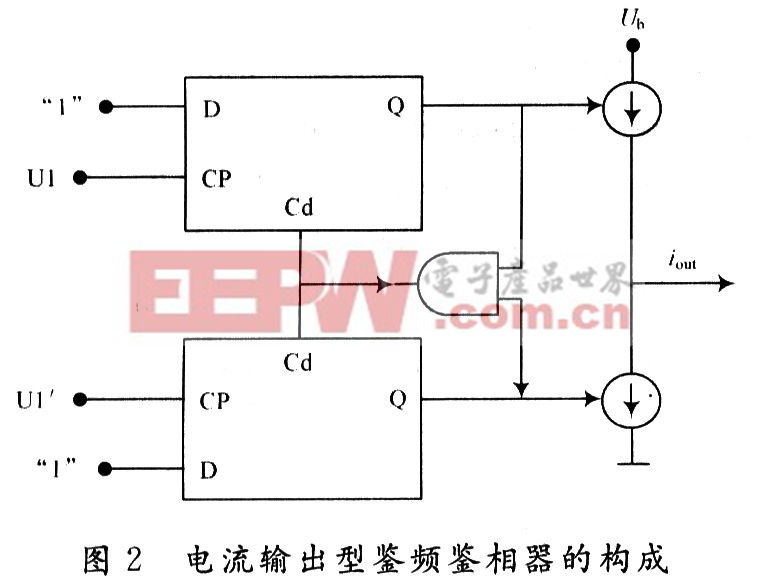

通常锁相环芯片都同时集成鉴相器和分频器,如ADI公司的ADF4106。该芯片鉴相器采用电荷泵输出的鉴相器。图2为一个电荷泵输出鉴相器的原理图。

这种鉴相器由两个D触发器、一个与门和两个电流源构成,不仅可以鉴相,也可以鉴频,同时由于它采用电流源输出,克服了电压输出型鉴频鉴相器增益变化的不足。该鉴相器的输出电流与相位误差关系为iout=Kdθe/Rb,其中:Rb为鉴相器电压电流转换器固有的跨阻。分频器的作用是将VCO产生的输出信号频率除以N,然后输入鉴相器与参考信号进行比较。仿真时,直接采用ADS提供的元件Divide by N来实现,设其分频比N=70。

2.3 低通滤波器

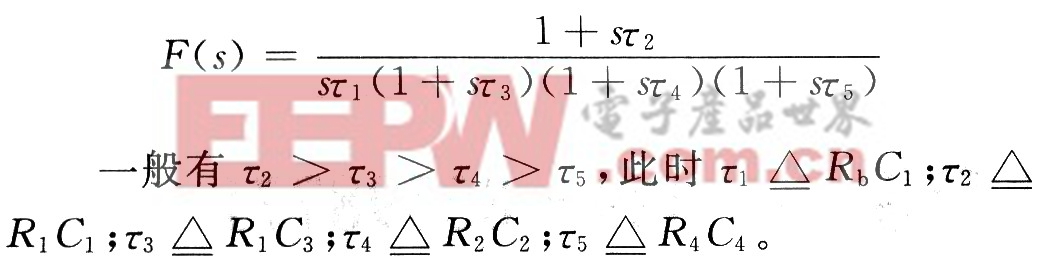

环路滤波器的设计是锁相环设计的关键。本设计中需要跟踪一个频率斜升信号。根据锁相原理,要跟踪此类信号,必须二型以上环路。本设计中环路滤波器采用四阶二型无源环路滤波器,由于电荷泵型鉴相器的输出为电流,所以该环路等效于一个二阶有源比例积分滤波器加两级辅助滤波。辅助滤波用于滤除参考信号馈通。环路传输函数F(s)可以近似表示为:

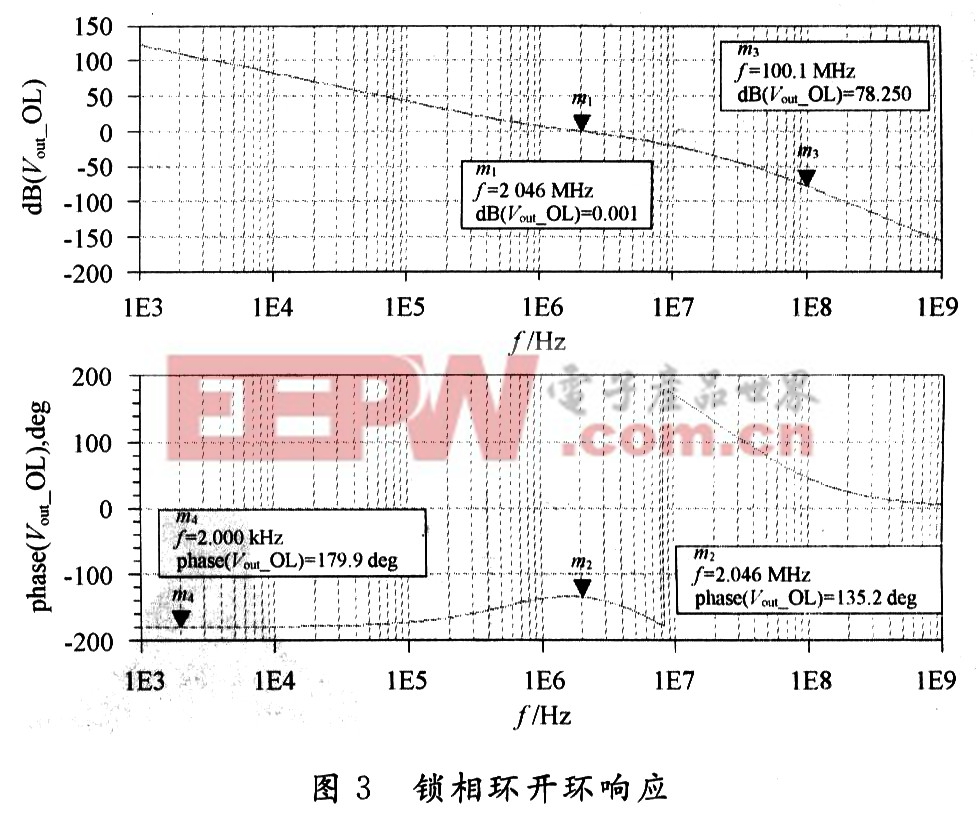

根据鉴相频率为100 MHz,这里选择截止频率ft为2 MHz。根据稳定性原理,通常选择![]() 为5~10倍ω3,ω5为3~8倍ω4,而ω1的选取则是保证环路幅频响应在ft处过零点。在ADS环境下,对模型中各元件大致设定一个初值及优化区间,然后进行优化设计,即可得到各元件值。最终锁相环开环响应如图3所示。

为5~10倍ω3,ω5为3~8倍ω4,而ω1的选取则是保证环路幅频响应在ft处过零点。在ADS环境下,对模型中各元件大致设定一个初值及优化区间,然后进行优化设计,即可得到各元件值。最终锁相环开环响应如图3所示。

分频器相关文章:分频器原理 鉴相器相关文章:鉴相器原理

评论