基于DSP的声雷达信号采集系统

在声雷达系统中,发射机定向发出不同频率的声信号,随后接收不同距离上的回波信号,利用回波中频率的偏离可以测定风速、风向随高度的变化。本文介绍的基于美国模拟器件公司的DSP ADSP-TS201S和ADC AD7864的信号采集系统能够满足这些要求。

本文引用地址:https://www.eepw.com.cn/article/150308.htm系统的设计

1 系统功能模块划分

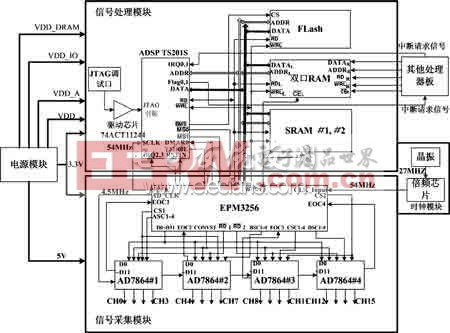

声雷达信号采集系统主要由信号采集、信号处理、电源和时钟四部分组成,如图1所示。信号采集模块由CPLD和4片ADC组成,负责完成A/D转换;转换后的数据送至信号处理模块,DSP ADSP-TS201S负责数据的接收和处理,两片512k×32b的SRAM完成了多帧数据的存储任务;一片双口RAM为ADSP-TS201S和其他处理器板交换信息提供了方便的接口,Flash用于存储用户的应用程序。电源模块为其他模块提供正常工作所需的电压。在时钟模块中,由晶振产生的27MHz时钟通过倍频芯片得到54MHz时钟后进入CPLD,它一方面作为ADSP-TS201S的系统时钟SCLK,另一方面在CPLD内12分频之后作为AD7864的工作时钟信号AD_CLK。

本系统之所以采用ADSP-TS201S芯片源于其强大的处理能力,可以对大量的回波数据作实时处理。它在600MHz的内核时钟下可以达到每秒48亿次乘累加(MAC)运算和每秒36亿次浮点运算(FLOP),具有比同类处理器高出50%~100%的处理能力。它内部集成了24Mb的存储器,这种片内大存储量与高达33.6Gb/s的内部带宽相结合,是提高性能的关键。其外部64位数据总线和32位地址总线时钟最高可达125MHz。

图1 信号采集系统电路图

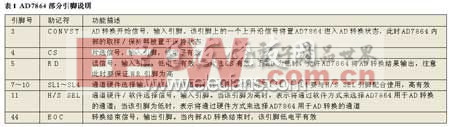

声雷达系统中需要多通道同时采样,AD7864芯片的高速多通道和同时采样特性满足了系统的要求,简化了硬件设计,它的转换精度为12位,吞吐量最高可达520KSPS,单通道转换时间最快可达1.65μs,采样/保持时间为0.35μs。此外,其单电源和低功耗特性(最低可达20μW)也满足了系统的要求。

系统工作时,首先是由后端处理器板向ADSP-TS201S发出中断信号,通知TS201从双口RAM中读取命令字。根据命令字,TS201通过CPLD控制前端的ADC进行数据采集并利用DMA方式读取数据,处理好的数据存储于双口RAM中,TS201也通过中断方式来通知后端处理器板来读取数据并显示。

2 硬件电路设计

在时钟电路的设计中,晶振和倍频芯片的电源与本板电源之间要用电感或磁珠来隔离,防止它们对系统电源产生耦合干扰。为了抑制由电压波动引起的电流涌动和低频干扰,两者的电源引脚处要加上一个10μF的钽电容,0.1μF的用于抑制高频干扰的小电容也是必不可少的,而且要贴近管脚放置。此外,还应注意不要在时钟芯片底下走线,防止相互耦合干扰。倍频芯片输出端可以加一个33Ω的匹配电阻,以减少输出电流,提高时钟波形质量。为了减少EMI辐射和时钟抖动,要尽量减少过孔的使用。

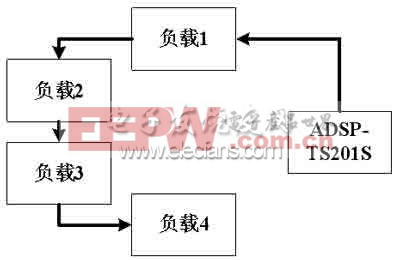

(a)环形结构

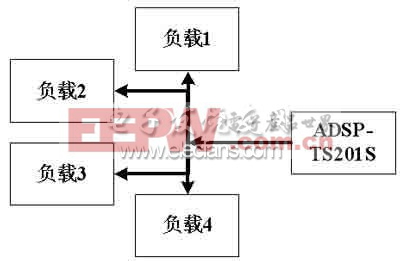

(b)星形结构

高频下总线的设计也是需要注意的,尤其是在系统中总线负载较重的情况下,不适当的设计会限制总线只能在低频下工作,甚至无法读取数据。由于环形结构上任一负载的变化都会影响到其他负载的工作,本设计中采用了星形总线结构,如图2所示。在布线过程中考虑到DSP总线的驱动能力,严格的将每根信号线的长度控制在6英寸左右。实践证明,采取的以上措施是必要而且正确的。

ADSP-TS201S和AD7864对电源的要求都非常高,例如,S201要求500MHz核时钟时,它的4个电源VDD、VDD_A、VDD_IO和VDD_DRAM的精度为±5%,因此,系统中采用了输出电压精度可达±1%的TPS54350作为电源芯片。

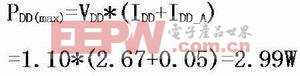

ADSP-TS201S的功耗可通过如下计算得到。以500MHz为例,VDD域消耗的电流可达2.67A,由式(1)可得,加上VDD_A的电流,内核最大功耗为 2.99W。

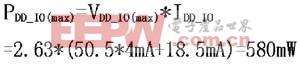

由式(2)可得,VDD_IO域上的最大功耗为580mW。

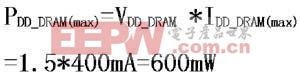

由式(3)可得,内部RAM的最大功耗为600mW。

基于以上数据,由式(4)可得,ADSP-TS201S在500MHz下的总功耗为4.17W。

(4)

ADSP-TS201S的功耗还是比较大的,因此在设计时要为散热片或风扇留出空间。电源部分的高频噪声会影响ADSP-TS201S的工作速度,尤其是电压低于1.5V的部分,所以在TS201的电源输入引脚附近要用低ESR的陶瓷贴片电容滤波,此外VREF和SCLK_VREF引脚也需要注意滤波。

由于系统是包括ADC的数模混合电路,设计中应注意以下问题。在AD7864和CPLD附近大面积的覆铜可以屏蔽外部对模拟信号的干扰,同时AD7864的电源引脚、参考电压输入引脚、VDRIVE引脚与模拟地之间要加0.1μF的贴片电容去耦;数字信号走线和模拟信号走线要分开布放;整板的数字地和模拟地要分开且保证单点相连,相连点选择在了模数信号汇集的地方;为AD7864供电的5V电源需要远离AD7864。

在调试过程中发现,如果不为ADSP-TS201S的JTAG口加驱动芯片,切入硬件仿真环境时Visual DSP会出错,所以建议即使是单片ADSP-TS201系统也要加一片驱动芯片,如TI公司的74ACT11244。

为了提高系统的灵活性,建议为ADSP-TS201S的SCLKRAT0~2(用于选择倍频系数)和DS0~2(用于选择总线驱动能力)引脚分别提供上拉和下拉两种选择,根据调试中的实际情况灵活配置。

评论