现代FPGA设计的能源优化方案

4 低功耗研究

4.1 降低电压

降低电压是减少功耗的最有效方式之一,而且随之而来的性能下降对许多并不要求最高性能的设计来说是可以接受的。不过,目前FPGA的工作电压范围很小,在某些电压敏感型电路上还不能使用。

在Xilinx研究实验室,CLB电路被重新设计成能在降低许多的电压下工作,以便在较低功耗情况下提供宽裕的性能权衡余地。例如,对于90nm工艺,电压下降200mV可降低功耗40%,最高性能损失25%;电压下降400mV可降低功耗70%,最高性能损失55%。

4.2 细粒度电源开关

可编程逻辑设计特有的开销之一是并非所有片上资源都用于给定的设计。可是,未使用的资源保持供电状态,并以漏电功耗的形式增加了总功耗。模块级电源开关可分别关掉未使用模块的供电。每个模块通过一个电源开关耦接到电源。开关闭合时,该模块工作。开关断开时,该模块从电源有效断开,从而使漏电功耗降到1/50~1/100。电源开关的粒度可以小到单个CLB和Block RAM。在设计中,这些电源开关可以通过配置比特流进行编程,也可由用户直接控制或通过访问端口控制。实际设计的基准测试结果表明,细粒度电源开关可减少漏电功耗30%。

4.3 深睡眠模式

便携电子产品的主要要求之一是器件空闲时功耗极低或无功耗。以Xilinx Spartan-3A FPGA为例,该芯片可通过进入休眠模式来达到此目的,这需要外部控制,苏醒缓慢,且不能恢复FPGA状态。设计动态控制上述细粒度电源开关,令其关闭所有内部模块供电,仅保留配置和电路状态存储组件为供电状态。这样形成的状态是一种深睡眠模式,其漏电功耗为额定功耗的1%~2%,保存FPGA状态,退出此模式仅需数微秒。

4.4 异构架构

电路的最高时钟频率取决于其时序关键型路径的延迟。非关键型路径的速度可以较慢而不影响整体芯片性能。在大型系统中,可以有几个速度关键型模块(如处理器中的数据通路),其他模块可以是非关键型(如缓存)。

当今的FPGA就功耗和速度而言是相同的;每个CLB 均有同样的功耗和速度特性。异构架构可降低功耗,这种架构包含一些低功耗(同时也较慢)的模块,方法是在低功耗模块中实现非关键型模块。这样做不影响整体芯片性能,因为时序关键型模块并未损失性能。

创建异构架构的一种方法是,分配两条核心供电轨,即一条高电压轨(VDDH)和一条低电压轨(VDDL)。FPGA的每个器件用嵌入式电源开关选择这二者之一,并相应采用高速度或低功耗特性。设计的详细时序确定之后,电压选择便告完成,所以只有非关键型模块才应以VDDL供电。

创建异构架构的另一种方法是,将FPGA分成不同的区,并将这些区分别预制为具有高速度和低功耗特性。可以用不同电源电压、不同阈值或通过若干其他设计权衡条件来实现这些区。要避免性能下降,设计工具必须将设计的时序关键型器件映像成高速度区,而将非关键型器件映射成低功耗区。

4.5 低摆幅信令

随着FPGA容量增加,片上可编程互连的功耗越来越大。减少这种通信功耗的一种有效方法是使用低摆幅信令,其中导线上的电压摆幅比电源电压摆幅低得多。现今,低摆幅信令常见于在高电容性导线(如总线或片外链接)上进行通信的情况。低摆幅驱动器和接收器比CMOS 缓冲器更复杂,所以占用更多芯片面积。但是,随着片上互连逐渐成为总体功耗的较大组成部分,低摆幅信令的功耗优势将证明增加设计复杂性是值得的。当然,FPGA用户不会看到内部信号电压的差异。

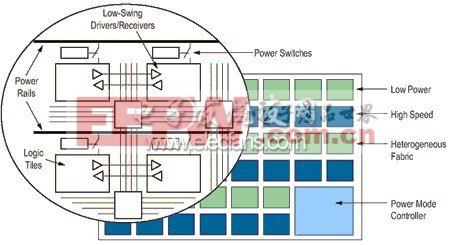

图3所示为具有上述某些概念的FPGA架构,其可编程异构架构由高速度和低功耗两个区组成。一个片上功耗模式控制器可管理各种降功耗模式,即深睡眠模式、悬挂模式和休眠模式。在架构内部,可以用专用的供电开关关掉每个逻辑块的电源。通过布线架构的通信信号流经低摆幅驱动器和接收器,以降低互连功耗。

图3 具有多种降低功耗解决方案的概念架构

5 结论

除了目前用于现代FPGA设计的能源优化方案,一些用户设计决策也可以产生显着的功耗效益。可以预见,未来的新技术中会有更大胆地遏制功耗的架构解决方案,从而使新的FPGA应用成为可能。

评论