基于NAND Flash的数据存储系统设计

引言

传统的存储设备虽然具有价格低廉的优势,但是在高温、高速、高冲击的测试环境中,往往存在设备存放空间有限、测试参数较多、采集速率高、环境复杂等因素。为了得到准确的测试数据,对存储设备的性能也提出了较高的要求,如高存储速度、大存储容量、小巧轻便、抗冲击等。此时传统的存储设备便无法完成复杂环境测试数据的存储任务。为解决这个问题,本文设计了基于NAND Flash的数据存储系统,该系统采用Xilinx公司提出的灵活、高效、低成本的解决方案SOPC,把通用的RISC处理器MicroBlaze与用户设计的特定功能逻辑电路集成到FPGA上,在FPGA的控制下将数据存储到NAND Flash存储设备中,实现了一个基于SOPC方案的嵌入式数据存储系统。

NAND Flash存储设备是Flash内存的一种,其内部采用非线性宏单元模式,为固态大容量内存的实现提供了廉价有效的解决方案。NAND Flash存储器具有体积小、功耗低、读写速度快等优点,适用于大量数据的存储,被广泛应用到数码相机、MP3、U盘等嵌入式产品中。

1 系统整体设计方案

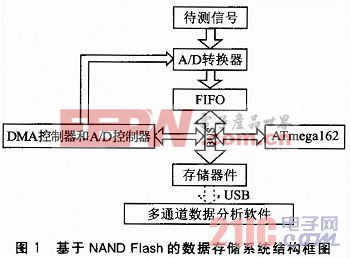

基于NAND Flash的数据存储系统结构框图如图1所示。

本文采用Samsung公司的NAND Flash芯片K9F4GOSUOA作为主要存储器件,控制器件使用Atmel公司的ATmega162和Xilinx公司Spartan-3E系列的XC3S500E,结合对NAND Flash的读、写、擦除等操作进行时序配置。A/D转换芯片使用Maxim公司的MAX1308。另外,为实现通过USB总线将数据从采集设备传送至PC,采用FTDI公司的FT245R芯片作为USB2.0接口控制器;并以LabVIEW为平台设计开发了专用“多通道数据分析软件”,用于对存储系统中数据后期的分析与处理。

2 NAND Flash阵列式存储原理

Flash存储器编程是以页为单位,单片NAND Flash的单页编程操作时,命令锁存信号CLE向端口写入编程操作命令,地址锁存信号ALE写入操作块地址,并传输2 KB数据到数据寄存器后,Flash进入编程阶段。此时其端口R/B信号被拉低,显示Flash正处于忙工作状态,直到编程结束,这段时间系统不能对该Flash再进行任何操作,一般该阶段典型的时间为200μs。如果使用单片Flash存储器进行存储,则需等待编程结束后才能再写入数据。这样大量的时间耗费在编程过程中,极大限制了系统存储速度的提高。

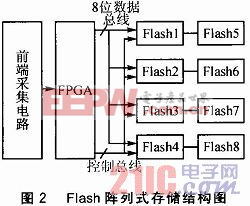

为提高系统的存储容量和存储速度,系统使用8片NAND Flash存储器,每4片为一组构成一个总线宽度为8位的存储阵列。控制信号中除设置独立的片选信号CE外,其他的控制信号为8片共用;两组Flash共用数据总线,存储数据时先对第一组Flash进行存储操作,待第一组存储完毕后再对第二组进行数据存储操作。Flash阵列式存储结构图如图2所示。

评论