Xilinx UltraScale 架构—业界首款ASIC级All Programmable架构

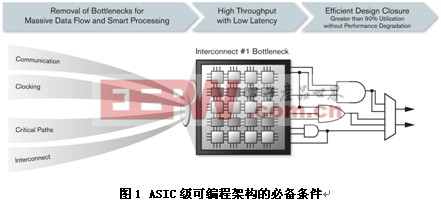

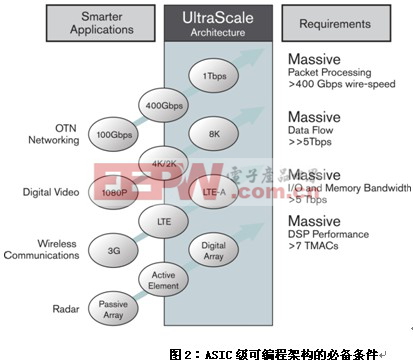

现在,人们需要采用一种创新型架构来管理数百Gbps的系统性能,以实现全线速下的智能处理能力,并扩展至Tb级性能和每秒10亿次浮点运算水平。实现上述要求的必要条件并非仅仅是改善每个晶体管或系统模块的性能,或者增加系统模块数量这么简单,而是要从根本上提高通信、时钟、关键路径以及互连性能,以满足行业新一代高性能应用(如下图所示)对海量数据流和智能数据包、DSP或图像处理等的要求。

本文引用地址:https://www.eepw.com.cn/article/147355.htm

UltraScale™ 架构通过在完全可编程的架构中应用最先进的ASIC 技术,可应对上述这些挑战。该架构能从20nm平面FET结构扩展至16nm鳍式FET晶体管技术甚至更高的技术,同时还能从单芯片扩展到3D IC。UltraScale架构不仅能解决系统总吞吐量扩展和时延方面的局限性,而且还能直接应对先进工艺节点上的头号系统性能瓶颈,即互连问题。

UltraScale™架构具有无与伦比的高集成度、高容量和ASIC级系统性能,可满足最严苛应用的要求。UltraScale架构经过精调可提供大规模布线能力并且与Vivado®设计工具进行了协同优化,因此该架构的利用率达到了空前的高水平(超过90%),而且不会降低性能。

为您量身定做的新一代架构

赛灵思对UltraScale架构进行了数百项设计提升,并将这些改进实现有机结合,让设计团队能够打造出比以往功能更强、运行速度更快、单位功耗性能更高的系统。

UltraScale架构与Vivado™设计套件结合使用可提供如下这些新一代系统级功能:

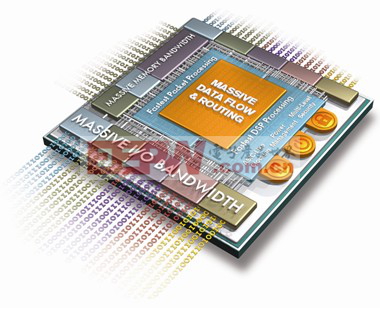

针对宽总线进行优化的海量数据流,可支持数Tb级吞吐量和最低时延

高度优化的关键路径和内置高速存储器,级联后可消除DSP和包处理中的瓶颈

增强型DSP slice包含27x18位乘法器和双加法器,可以显著提高定点和IEEE 754标准浮点算法的性能与效率

第二代3D IC系统集成的晶片间带宽以及最新3D IC宽存储器优化接口均实现阶梯式增长

类似于ASIC的多区域时钟,提供具备超低时钟歪斜和高性能扩展能力的低功耗时钟网络

评论