随着 PCI Express 在高端 FPGA 中变得司空见惯,让我们看看 FPGA 供应商如何轻松实现该技术。特别是,我们更仔细地研究了赛灵思的 PCI Express 解决方案。PCI Express 1 - 连接器PCI Express 通常有两种尺寸:1 通道和 16 通道,其中 1 通道用于普通主板,16 通道用于显卡。连接器1 通道连接器有 36 个触点,排列成两排,每排 18 个触点。这是俯视图。在 36 个触点中,只有 6 个对数据传输有用,其余是电源引脚和其他辅助信号。 6 个功能触点以

关键字:

FPGA PCI Express接口 赛灵思

根据英特尔官方的公告,2024年1月1日起,可编程解决方案部门(PSG)将独立运营,并计划2年内开启IPO。值得一提的是,英特尔的PSG其实就是以2015年5月达成收购协议的Altera为主体,从当年花费167亿美元成为英特尔最大一笔收购,到现在要独立运营甚至上市套现,种种操作背后蕴含了哪些原因我们不得而知,不过这笔投资的回报价值几何也许能终见分晓。 在半导体行业,作为霸占销售额榜首位置最久的公司,英特尔在收购方面表现得一直很积极,但从另一个角度来看,英特尔的收购交易获得较高评价的也不多,很多交易即使计算

关键字:

英特尔 PSG FPGA Altera 赛灵思 Lattice

赛灵思:更智能的解决方案集锦赛灵思(Xilinx)具备更智能的网络专家,能帮客户最大限度地实现未来设计的价值,充分发挥 Xilinx All Programmable FPGA 和 SoC 产品的作用,从而帮助客户领先同类竞争对手整整一代的水平。Xilinx 面向网络和数据中心的更智能的解决方案针对三大细分市场:(1)更智能的无线 HetNet;(2)更智能有线网络,包括边缘和电信级以太网;(3)更智能的数据中心。赛灵思更智能的解决方案可实现以下目标:(1)系统性能提升;(2)BOM 成本削减;(3)总功

关键字:

赛灵思 以太网 有线网络 智能

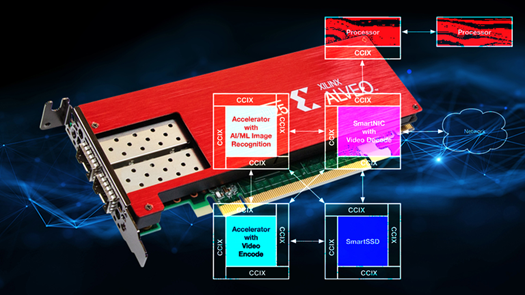

IT之家 4 月 6 日消息,2020 年,赛灵思发布了其首款“一体化 SmartNIC(智能网卡)平台”——Alveo U25 的数据中心加速卡,在单颗器件上实现了网络、存储和计算加速功能的融合。作为 Xilinx Alveo 系列的后继产品,AMD 今天推出了一款新的数据中心专用加速卡 ——Alveo MA35D。与 Alveo U30 一样,MA35D 是专为数据中心设计的纯视频编码卡,目前已经向其合作伙伴提供了样品。简单来说,最新一代的 Alveo 加速卡有着比其前身

关键字:

赛灵思 Xilinx

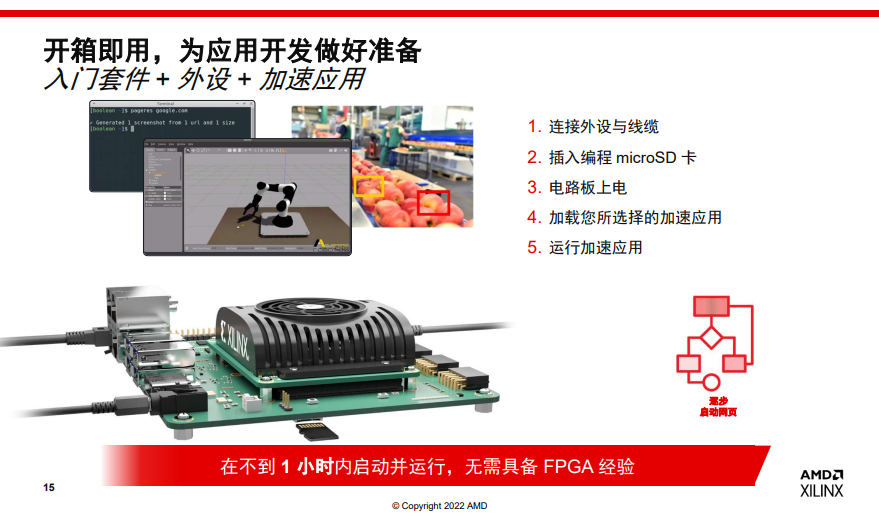

AMD(纳斯达克股票代码:AMD)上周在深圳成功举办AMD 赛灵思技术日活动。AMD 高级副总裁、大中华区总裁潘晓明发表了题为《同超越,共成就》的主题演讲,AMD 大中华区销售副总裁唐晓蕾以《自适应计算加速创新落地》为主题发表了演讲。活动上,AMD 多位技术专家带来了针对 Versal™ ACAP 、Kria 系统模块(SOM)和Zynq RFSoC 自适应 SoC 的概览,以及 AMD 商用 PC 方案的最新产品与方案动态,还围绕智能汽车、智能制造、工业、机器视觉、医疗成像、专业音视频等领域,分享了基于

关键字:

AMD 赛灵思 技术日

赛灵思已推出一系列工业物联网解决方案,马达控制为其中一种应用。这类应用之一便是含马达与电源供应器的电子驱动开发平台(EDDP)马达控制套件。平台内部装载开发及评估三相马达控制应用时所需的所有软硬件组件。 主要硬件组件包含Trenz Electronic GmbH用作马达驱动板的TEC0053、Digilent Inc.用作参考控制器板的Arty Z7-10,和Anaheim Automation用作参考马达的BLDC马达。主要软件组件为Vivado SDSoC所实作的Field Control Al

关键字:

安富利 赛灵思 马达控制

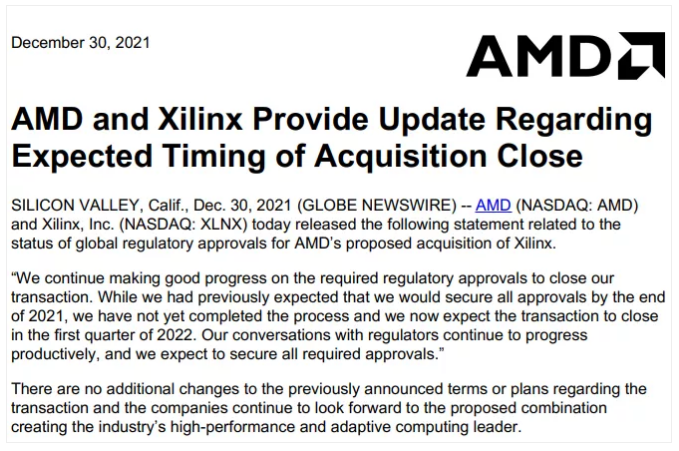

近日,AMD和赛灵思公司发表了声明,AMD预计将在今年第一季度完成对赛灵思公司的收购。声明表示,“我们继续在完成交易所需的监管批准方面取得良好进展。虽然我们之前预计我们将在2021年底之前获得所有批准,但我们尚未完成该流程,我们现在预计交易将在2022年第一季度完成。我们与监管机构的对话继续富有成效,我们希望获得所有必要的批准。”与英伟达以400亿美元收购ARM类似,完成这笔交易需要世界各地的监管机构审批才行。不过与英伟达需要面对来自相关监管机构的严格审查不同,AMD面临的阻力显然比英伟达要小很多。目前A

关键字:

AMD 赛灵思 数据中心

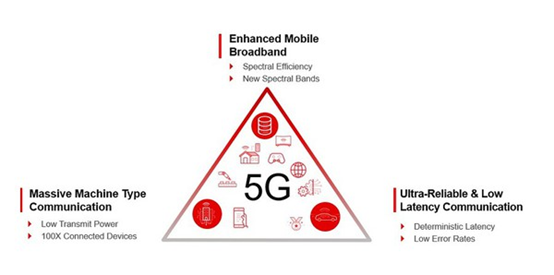

随着5G基础设施和装置设备的部署,5G已从概念转变成为现实;5G经济显然不会只是3G或4G的复制品。新的挑战需要能自行调适的解决方案,既要可以处理多样化的需求,同时也要能够随市场需求的变化而持续演进发展。Zynq UltraScale+ RFSoC DFE因其架构上整合了比传统软件化逻辑(soft logic)更多的硬件化IP逻辑,使得其在保持灵活应变价值的同时,还能媲美客制化的ASIC在成本和功耗上的竞争力,因此能轻松应对这些挑战。 5G面临的前线挑战日益提高的无线电效能和复杂性无线电单元(

关键字:

Zynq RFSoC 5G 赛灵思

边缘运算主要包含以下四个部分,低时延、AI算力、低功耗以及安全和保密,这四者是边缘自主非常重要的组成部分,也是边缘区别于工业和IoT的一个主要特点,也就是用运算资源来支持边缘的自主,使它能够独立于云端。 赛灵思Versal AI Edge系列资深产品线经理 Rehan Tahir赛灵思Versal AI Edge系列高级产品线经理Rehan Tahir指出,当赛灵思在2018年引入Versal ACAP的时候,首先推出的是Versal Core和Prime系列,用于云端和网络,然后推出了Vers

关键字:

赛灵思 FPGA ADAS

作为第四任赛灵思的CEO,上任三年多的Victor Peng在交易后首次面对中国的媒体时,除了总结自己上任三年来的成绩之外,更是重点的回应了对合并后企业的愿景

关键字:

赛灵思 FPGA AMD

与普通的 NIC 不同,SmartNIC 将会对 PCIe 总线提出更高的要求。CXL 和 CCIX 等第五代 PCIe 和协议在此背景下应运而生。不久之后,我们将能共享一致性存储器、高速缓存,并建立多主机点对点连接。 正文:过去三十年间,基于服务器的计算历经多次飞跃式发展。上世纪 90 年代,业界从单插槽独立服务器发展到服务器集群。紧接着在千禧年,产业首次看到双插槽服务器,再后来,多核处理器也问世了。进入下一个十年,GPU 的用途远远超出了处理图形的范畴,我们见证了基于FPGA的加速器卡的兴起

关键字:

PCIe 5 FPGA 赛灵思

Lisa Su和Victor Peng,两位硅谷鲜见的华裔而不会说中文的CEO达成了也许是半导体历史上最特别的一笔交易。赛灵思这家以发明FPGA而快速成长的企业,这次也许通过出售自己让FPGA作为主芯片的时代就此终结。

关键字:

FPGA 赛灵思 AMD

10月27日消息 本月初,有消息人士表示 AMD 正在就收购赛灵思(Xilinx)公司展开深入谈判。据路透社今日消息,AMD 周二表示,已经同意以350亿美元全股票交易收购赛灵思 (Xilinx)。AMD 预计该交易将在2021年底完成,合并后的公司将拥有13,000名工程师,采取全部外包的生产策略,主要依靠台积电进行生产。IT之家知悉,根据协议,赛灵思股东可用一股赛灵思普通股换取约1.7股 AMD 普通股,对赛灵思估值为每股143美元,较其10月26日收盘价114.55美元溢价约24.8%。AMD 股东

关键字:

AMD 赛灵思

继前段时间英伟达宣布将以400亿美元收购ARM之后,又一桩并购案被华尔街日报爆出:AMD有意以超过300亿美元的价格收购......

关键字:

AMD 赛灵思 Xilinx

赛灵思介绍

赛灵思公司____________全球完整可编程逻辑解决方案的领导厂商

(2009年3月)

赛灵思公司(NASDAQ: XLNX)是全球完整可编程逻辑解决方案的领导厂商,占有该市场超过一半以上的份额,2008年度赛灵思公司的收入为19.1亿美元。赛灵思屡获殊荣的各种产品,包括硅片、软件、IP、开发板、入门套件,可使设计者为多种终端市场提供应用并大大缩短上市时间,包括航天/国防、汽车、 [

查看详细 ]

关于我们 -

广告服务 -

企业会员服务 -

网站地图 -

联系我们 -

征稿 -

友情链接 -

手机EEPW

Copyright ©2000-2015 ELECTRONIC ENGINEERING & PRODUCT WORLD. All rights reserved.

《电子产品世界》杂志社 版权所有 北京东晓国际技术信息咨询有限公司

京ICP备12027778号-2 北京市公安局备案:1101082052 京公网安备11010802012473