手把手课堂:Xilinx FPGA设计时序约束指南

传输时间与 OFFSET 约束

本文引用地址:https://www.eepw.com.cn/article/119144.htm信号从 A 点到达 B 点所用的时间称为传输时间。它取决于传输介质中光传播的速度。例如,PCB 电路板上的走线以 6~7 皮秒/ 毫米来传输信号。可采用多种方法来确定这一时间值,例如进行仿真,或在材料介电常数与走线几何结构已知的情况下,列方程求解。在芯片内,信号的行为方式也很类似,不过也会因通过缓存器、反相器、逻辑和互联等有源电路而发生延迟。

传输时间是可测量的,通常用示波器来测量。当路径上无有源元件时,传输时间一般不会有太大变化。若路径在芯片内,则晶体管的作用会使路径延迟在最大值与最小值之间变化。设计需同时满足二者的时序要求。

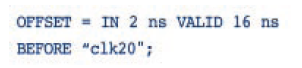

为告诉工具数据何时到达特定位置,需使用另一种名为“OFFSET_IN”的约束。“OFFSET_IN”约束在时钟和数据进入器件时,对其关系进行了定义。以如下约束为例:

该约束告知工具,数据将在 clk20 脉冲上升沿之前 2 纳秒建立在 PAD 上,并在到达后 16 纳秒内保持有效。该约束只对那些进入由 clk20 或其衍生(衍生约束)提供时钟的寄存器的 PAD 有效。

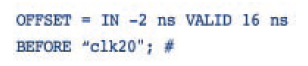

OFFSET 要求在 clk20 上有一个PERIOD 约束,这样才能理解时钟结构。如下这样也可接受:

不过,该约束不会检查保持时间,因不清楚数据何时会从 FPGA 的引脚结束。若数据在时钟脉冲边沿 2 纳秒之后才建立,则使用如下方案:

OFFSET_IN 适用于进入器件的时钟与数据之间的关系,另一种常见的OFFSET_OUT 约束定义时钟在 FPGA 输入处发生跳变后数据离开器件所需的时间。以下为常见的 OFFSET_OUT 用法:

![]()

该约束告知工具,需确保输入时钟在 FPGA 输入跳变后 3 纳秒时长后,数据出现在 FPGA 的输出引脚上。该约束仅应用于由 clk20 或其衍生(衍生约束)提供时钟的寄存器驱动的 PAD。OFFSET 要求在 clk20 上有 PERIOD 约束,这样才能理解时钟结构。保持时间不受 OFFSET_OUT 的约束。

若需要数据在时钟脉冲边沿前 2 纳秒到达FPGA 输出,则使用:

![]()

分组与分组名称

时间分组是用来识别对于同步元件间的路径集或连线集的约束的一种方式。向时序分组添加组件,应使用 TNM、TNM_NET 或 TIMEGRP。

通过定义分组并给定分组之间的时序要求,可对路径进行约束。部分约束不需要时序分组,如 NET MAXDELAY。这一最大延迟 (MAXDELAY) 属性定义了一条连线上允许的最大延迟。

时序名称

向用户定义的分组添加组件,可这样处理:

在此,“TNM”为保留字,用于定义时序分组的名称。

在这种情况下,object_name 为带分组元件或信号的名称,predefined_group 为可选关键词,标示符可以是字母、数字和下划线的任意组合。不能使用诸如 FFS、LATCHES 或RAMS 这样的保留字。该变量对大小写敏感。(TNM=abc 不等于 TNM=ABC)。

可将 TNM 应用于任何连线、元件引脚、原语或宏。组件可加入一个以上的分组。例如,my_ffs_group TNM 中可含有 my_ff组件。同样,my_ffs_group2 TNM 也可包含 my_ff 组件。要创建分组,请使用:

![]()

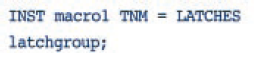

为时序目的,可在分组中包含任何关键词元件。在本例中,NET CLOCK可追溯到触发器 (FFS)。这些触发器使用名称 clk_group 进行时序命名 (TNM)。然后,clk_group 就可以在TIMESPECS中使用了。也可使用实例创建分组,如:

fpga相关文章:fpga是什么

评论