手把手课堂:Xilinx FPGA设计时序约束指南

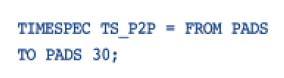

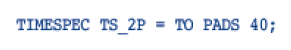

若不选定时间单位(纳秒、皮秒等),则工具将自动默认为纳秒。例如,可这样写约束:

本文引用地址:http://www.eepw.com.cn/article/119144.htm

也可只写From 或 只写To ,以使其更具一般性:

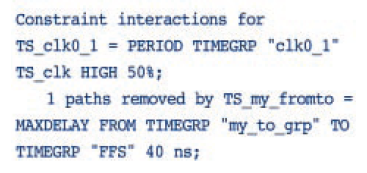

如前所述,工具将自动默认上文所述所有 FROM: TO 约束的优先级高于PERIOD 约束,除非另有规定。

除帮助查看时序约束迭代外,.tsi 报告还就如何改进通用约束文件 (UCF) 中的约束提供方法建议。该报告还会告知是否有路径受多重时钟域的约束。下面是约束迭代报告的例子:

在本例中,高优先级的 FROM: TO约束(仅一个)将优先于 PERIOD 约束应用。

建立和保持

在实际的同步数字系统中,数据必须先于进行采样的时钟脉冲边沿到达。达到这一目标所需的最短时间称为“建立时间”。除了先于时钟脉冲边沿到达外,数据必须在时钟脉冲边沿保持一定时间,这一时间称为“保持时间”。保持时间可

以为负,此时数据在时钟脉冲边沿到达前便已结束;可以为零,此时数据保持到时钟脉冲边沿采样;也可为正,此时数据保持到时钟脉冲边沿采样完毕后一段时间。

根据设计,在 FPGA 架构中,对所有速度等级,保持时间均不为正(或零或负)。这样可简化布局和布线,因数据只

需先于时钟脉冲边沿到达,并可在时钟脉冲边沿采样发生后即刻发生变化。数据超出最小建立时间的值称为时序裕量。时序裕量应总是为正。若报告上出现时序裕量负值,则说明建立时序尚未得到充分满足,数据到达太迟。

时钟路径本身也有延迟或偏移。因此,要分析时序,工具需计算出数据和时钟到达所分析触发器的时间。

约束违例的简便补救办法

重申一下:PERIOD 约束定义的是触发器等同步元件的时钟周期。可使用时序分析器来验证同步元件之间的所有路径是否满足设计的建立和保持时序要求。PERIOD 约束违例将以负的时序裕量显示在在时序报告,并说明到底是建立时间还是保持时间要求出现违例。所以若报告显示发生了建立时间违例时该作何处理?应找出两个所分析的同步元件间一条较快路径,或至少是某种方法来确保数据在合适时间内到达并保持足够长的时间,以便时钟脉冲边沿能够正确采样。若布局布线软件无法找到更快的路径,则可从 FPGA Editor 工具中手动进行布线。

不过这是最后的手段。在弄清楚不用它如何解决问题之前,请尽量不要使用这种方法。只使用 FPGA Editor 查看底层结构“知其所以然”,了解工具对设计的所做的处理,以达到让设计恰当的使用FPGA 资源来实现的目的。首先试试重构电路来满足设计的时序要求。一个比较简单的方法就是在路径上及早布置一个触发器。该技术即为流水线,它会增加信号的延迟,不过也可使信号值得到正确地采样。

若出现保持时间违例(数据在时钟脉冲边沿到来之前便已结束),则往往说明存在设计问题(架构不良)。数值只能

在时钟脉冲边沿发生变化,而不是之前。

若外部信号值在时钟脉冲边沿之前发生变化,则需使用 DCM 或 PLL 延迟时钟脉冲边沿,这样数据才能由新的延迟时钟正确采样。

有一种替代方法,就是在输入/ 输出模块中使用 IDELAY 元件,将数据移到时钟有效的位置上。

数据有效窗口与亚稳态时钟脉冲边沿之前的时间(建立)加上时钟脉冲边沿之后的时间(保持)即为“数据有效窗口”,也就是数据保持稳定,以进行正常采样的时间。若数据在此期间没有保持有效,则结果存在不确定性,或不可知。

不过,数据的有效时间未达到规定的长度,并不意味着触发器输出为亚稳态。亚稳态不同于不确定。若不能满足时序要求,则输出可能为随机的 1 或 0。亚稳态是指时钟脉冲边沿“几乎”能进行状态采集,而触发器输出则在时钟脉冲边沿之后的一段时间内处于某种中间状态(非 1 非 0)。亚稳态无法避免,因其为时钟脉冲边沿和数据几乎完全“错过”时的电路物理状态。

在设计合理的同步系统中,亚稳态不是什么问题。当出现异步情况(如敲击键盘上的一个键)或当两个同步时钟彼此异步时,亚稳态就会成为问题。一般而言,若出现异步情况,则需进行同步处理。

关于如何处理亚稳态的情况,这里有篇不错的专题文章: http://www.stanford.edu/class/ee183/handouts_

spr2003/synchronization_pres.pdf 。(要深入了解亚稳态,请查看本期第二篇文章 FPGA101)

fpga相关文章:fpga是什么

评论